Synopsys Foundation IP for UMC 40ULP & 28nm Processes

Accelerate your automotive and IoT SoC development with Synopsys Embedded Memories and Logic Libraries for UMC 40ULP, 28HLP, and 28HPC process technologies. As part of Synopsys' Foundry-Sponsored IP Program, the DesignWare Logic Library and Embedded Memory IP is available at no cost to qualified licensees.

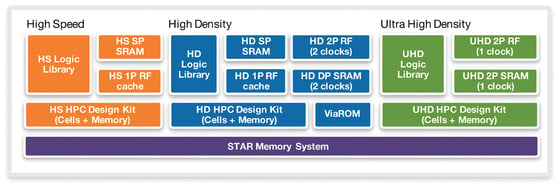

The High Performance Core (HPC) Design Kit for UMC processes contains a suite of high-speed (HS) and high-density (HD) memory instances and logic cells specifically designed to enable SoC designers to optimize their CPU, GPU and DSP cores for maximum speed, smallest area, lowest power, or an optimum balance of all three. In addition, the Synopsys Embedded Memories, Synopsys SLM SMS IP, and Synopsys SLM SHS IP are ASIL D Ready to ease your automotive IC’s ISO 26262 certification.

"Leveraging our success with Synopsys on dozens of prior process technologies, we are happy to bring their high-quality Synopsys IP to UMC’s 40LP, 28HLP and 28HPC processes so our mutual customers can achieve their stringent power, performance, and area objectives."

T.H. Lin, Division Director of IP Development and Design Support, UMC

Features:

- Embedded memories and logic libraries for UMC 40ULP are designed to operate at low voltages (0.9V), enabling IoT designs to dramatically reduce power dissipation

- Automotive designs can achieve industry-leading power, performance, and area (PPA) using IP that provides full set of ISO 26262 functional safety packages

- Embedded memories with built-in self-test STAR Memory System reduce overall SoC area and dynamic power

Figure 1: Integrated STAR Memory System reduces core area by ~7% and dynamic power by ~12%

Figure 2: Broad portfolio of Embedded Memories and Logic Libraries on UMC Processes