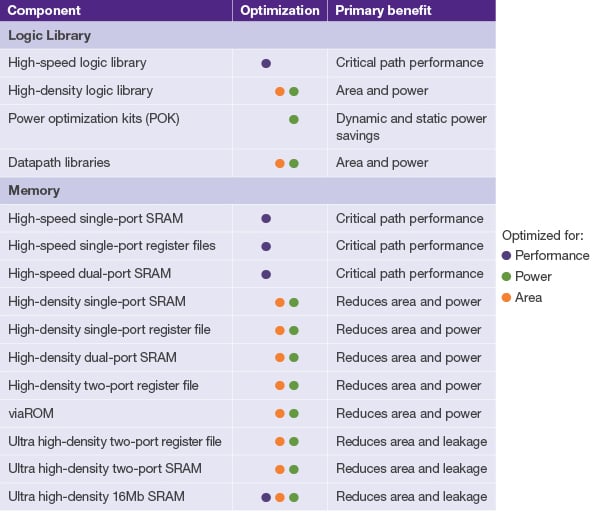

The Synopsys Duet Packages of Embedded Memories and Logic Libraries, part of Synopsys Foundation IP portfolio, deliver an integrated portfolio of logic libraries, memory compilers and memory test and repair capabilities. These packages combine high-performance and high-density SRAMs, register files, ROMs, standard cells, and Power Optimization Kits (POKs), providing all the essential elements for implementing a complete system-on-chip (SoC). A range of options—including overdrive/low voltage operation, process, voltage, and temperature corners (PVTs), high-density SRAMs, and multi-channel logic standard cells—enables designers to achieve optimal results tailored to their specific SoC applications.

Additionally, the High Performance Core (HPC) Design Kit offers a collection of high-speed and high-density memory instances and logic cells. This kit is specifically engineered to help SoC designers optimize CPU, GPU, and DSP cores for maximum speed, minimal area, lowest power consumption, or the ideal balance of all three.

Synopsys Embedded Memories and Logic Libraries are available for multiple foundries and process technologies. Find the best solutions for your SoC design needs: Foundation IP Selector.

Highlights & Datasheets

- All the elements needed to implement a complete SoC, including high-performance and high-density SRAMs, register files, ROMs, standard cells, and POKs

- High-density embedded SRAMs optimized to generate the absolute minimum area and power enable designers to achieve aggressive area and power budgets

- Multiple levels of memory power management features. Light Sleep, Deep Sleep and Shut Down modes enable array biasing with partial periphery shut down, full periphery shut down with data retention and a complete shut down without data retention

- Yield-optimized standard cells with multiple threshold voltage and channel length variants

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.