ウェアラブル・インフォテイメント・アプリケーション向けDesignWare IP

概要

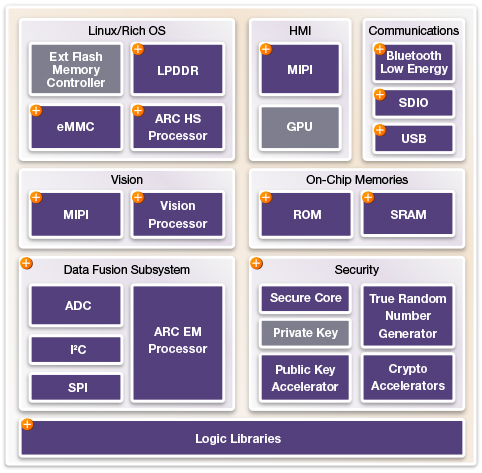

ウェアラブル・デバイスは、眼鏡、靴、腕時計などの物にリアルタイム・フィードバックを行う機能を付加することにより、日常生活にテクノロジーを取り入れています。こうしたデバイスは今後コネクテッド・ワールドの拡大に主要な役割を果たすでしょう。しかし、ウェアラブル・デバイスに搭載するSoCの設計には、長いバッテリ駆動時間、省面積、センサー・コンポーネントの改善(タッチ、音声、オーディオ、ビデオなど)をどのように実現するか、という設計上の大きな課題があります。

こうしたソリューションでは効率的なデータ処理が要となり、シノプシスの広範なDesignWare® IP製品群はこれらのSoC設計の課題に立ち向かうために最適化されています。

マウスカーソルを合わせるか、タップすると、DesignWare IPソリューションの詳細が表示されます。

Bluetooth Low Energy

- リンク層と物理層(PHY)

- 1ボルト未満の電圧供給で動作

- 統合型セキュリティ機能

- 最新のBluetooth low energy規格に対応

- 詳細はこちら >>

セキュリティ

- 鍵暗号コア、公開鍵アクセラレータ、TRNG

- セキュリティ・プロトコル・アクセラレータとコプロセッサ

- ハードウェアのセキュアなRoot of Trust環境を確立する組み込みセキュリティIPモジュール

- セキュアなブートおよび暗号用ミドルウェア

- 詳細はこちら >>

MIPI

- 相互運用性があるDSIおよびCSI-2コントローラ

- 消費電力が最適化されたD-PHY

- 低消費電力のGear3 M-PHY

- 標準規格に準拠

- 詳細はこちら >>

USB

- 面積の50%削減を実現するUSB femtoPHY - .16mm2

- 迅速な統合を実現する実証済みのUSBコントローラ

- USB充電検出機能のサポート

- 供給電源のゲーティングおよび極低スタンバイ電流のサポート

- 詳細はこちら >>

LPDDR

- DDR IPのコンフィグレーションを最適化するDDR PHYコンパイラ

- バッファ、受信機、ドライバの自動無効化をサポートし、消費電力の削減に対応

- x16およびx32 SDRAMのサポート

- 詳細はこちら >>

ビジョン・プロセッサ

- AIベースSoCのためのマシンビジョン/ディープラーニング・テクノロジ

- プログラマブルな畳み込みニューラル・ネットワーク(CNN)による物体検知エンジン

- OpenCVライブラリ、OpenVXランタイム/カーネルを備えた生産性の高いプログラミング・ツール

- 詳細はこちら >>

ARC HSプロセッサ

- ARC HS高性能32ビット・プロセッサ

- 1.6 GHz、電力60mW、面積 0.15mm2で3100 DMIPSを実現

- カスタマイズされた命令によりユーザーのHWアクセラレータを統合可能

- 詳細はこちら >>

SDIO

- SD 4.1、SDIO 4.1、eMMC 5.1仕様に準拠

- SD/eMMCで1ビット、4ビット、8ビットのカードをサポート

- クロックと電源のオン/オフ機能を備えた低消費電力オプション

- 詳細はこちら >>

eMMC

- SD 4.1、SDIO 4.1、eMMC 5.1仕様に準拠

- SD/eMMCで1ビット、4ビット、8ビットのカードをサポート

- クロックと電源のオン/オフ機能を備えた低消費電力オプション

- 詳細はこちら >>

SRAM

- 省電力モードを備えた高密度低リーク・メモリー

- 超低電圧動作

- リークパワーの70%削減を実現するディープスリープ・モード

- アクティブ・リークパワーを削減する長チャネル・デバイス

- 詳細はこちら >>

ROM

- 超低消費電力の非シグネチャ型ROM

- リークパワーを最大20%削減

- 詳細はこちら >>

ロジック・ライブラリ

- 静的電力を削減する「常時オン」の厚酸化膜Trライブラリ

- 動的電力の削減と省面積を実現するマルチビット・フロップ

- コア・リークパワーを最小化するPower Optimization Kit

- 超低電圧動作(公称電圧を40%下回る)

- 詳細はこちら >>

MIPI

- 相互運用性があるDSIおよびCSI-2コントローラ

- 消費電力が最適化されたD-PHY

- 低消費電力のGear3 M-PHY

- 標準規格に準拠

- 詳細はこちら >>

ハイライト:

- スリープ状態時に常時オン・ウェイクアップ回路のリークパワーを最小化する「常時オン」の厚酸化ロジック・ライブラリ

- 公称電圧を60%下回る低電圧にも対応する超高密度ロジック・ライブラリ

- クロックの読み込み、面積、リークパワーを最小化して動的/静的電力の向上を実現するマルチビット・フロップ

- 最適な性能を維持しながら電力消費量を削減することが可能なDesignWareロジックライブラリ向けPower Optimization Kit(POK)

- 高度なパワー・マネージメント機能を備え、0.9Vで動作するシングルピン1本による制御でリークパワーを最大70%削減可能なメモリー・コンパイラ

- 超低消費電力の非シグネチャ型ROMによりリークパワーを最大20%削減

- 最大限の性能効率を発揮し(DMIPS/mWおよびDMIPS/mm2)、高速なデータ/信号処理が必要とされる組み込み向けに最適なARC HSプロセッサ

- コンフィギュラブルで拡張性が高く、インスタンスごとに性能、消費電力、面積のバランスを最適化できるARC HSプロセッサの命令セット

- 畳み込みニューラル・ネットワークを実装する物体検知エンジンを含む、低コスト・低消費電力の専用ハードウェアとソフトウェア・ソリューションの柔軟性を組み合わせたプログラマブル/コンフィギュラブルなビジョン・プロセッサ

- 性能の向上とコード・サイズの削減を可能にする密結合メモリーとセンサー・インターフェイス・ペリフェラルとハードウェアアクセラレーターにより、センサーおよびコントロールIPサブシステムで大幅な省面積と低レイテンシーを実現

- DesignWare Universal DDRデジタル・コントローラおよび検証用IPとの組み合わせにより、LPDDR2/3に対応する包括的なマルチプロトコルのDDRインターフェイスIPソリューションを実現するDDR multiPHY IP

- リビジョン1.2規格に準拠したMIPI CSI-2およびDSIコントローラ 1レーン当たり最大2.5Gbpsで動作し、D-PHY PPIインターフェイスを備え、MIPI CSI-2は1~8データレーン、DSIは1~4データレーンをサポート

- 業界の主要なオンチップの実装を超える、最大14ビットの解像度と5MSPSの変換レートを実現するADC

- 統合が容易で、ローパワー機能付きのBattery Chargingをサポートする、実績ある認証取得済みのUSB 2.0コントローラおよびPHY

- コンパクトなBluetooth low energy向けリンク層および物理層(PHY)は、接続範囲がより広く、バッテリ駆動時間がより長いセキュアなワイヤレス接続を実現でき、ウェアラブル機器やスマートホームなどに最適

- 進化する脅威から保護する公開鍵アクセラレータ、真性乱数生成回路、セキュリティ・プロトコル・アクセラレータ、セキュアRoot of TrustなどのセキュリティIP