IoT applications increasingly require advanced sensing capabilities that extend beyond what traditional sensors provide. Functions such as face detection, voice and gesture recognition require an efficient combination of RISC and DSP processing. The Synopsys ARC® Data Fusion IP Subsystem is a complete, pre-verified, hardware and software solution optimized for a wide range of ultra-low power IoT applications. It is designed for fast and easy integration within a larger system context.

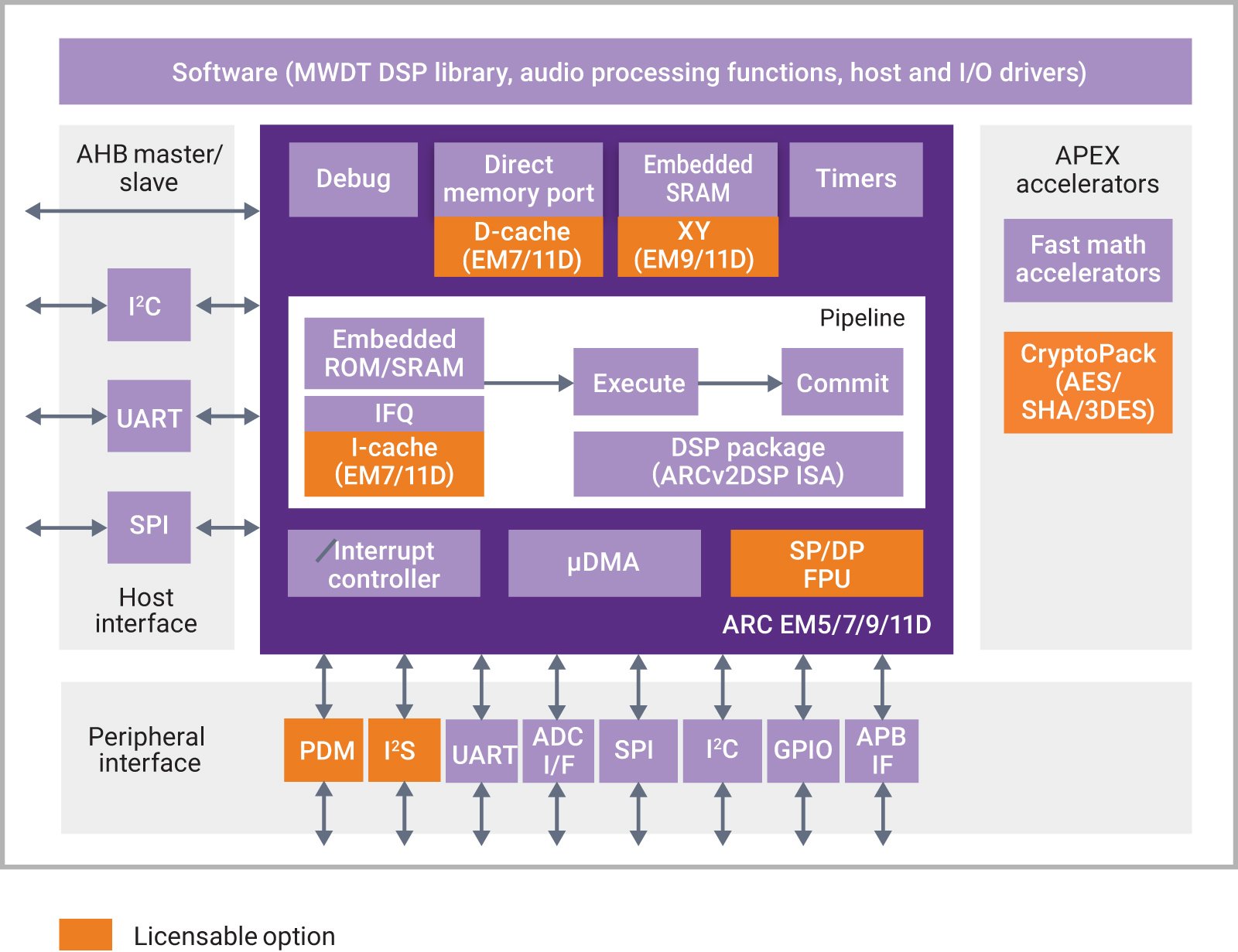

The fully configurable ARC Data Fusion IP Subsystem includes the choice of a low gate count and energy-efficient Synopsys ARC EM5D, EM7D, EM9D or EM11D processor for both RISC and DSP processing, accompanied by an extensive collection of I/O functions and fast math (trigonometric) accelerators. The software libraries of the subsystem contain small-footprint drivers for all I/O, plus DSP functions supporting signal processing. It also includes an audio processing software library of common functions, including gain control, mixer and sample rate converter. Tightly coupled PDM and I2S peripherals simplify integration of external audio devices and the hardware PDM interface implementation is 6X more energy efficient than the equivalent software implementation, with minimal gate count impact. The audio library and peripherals (PDM, I2S) are part of a voice/speech licensable option. The integrated solution is optimized for “always on” data fusion combining sensor, voice, gesture and audio processing typically implemented in IoT edge devices.

Figure 1: Synopsys ARC Data Fusion IP Subsystem integrated hardware and software solution

Highlights & Key Features

- Integrated, pre-verified hardware and software IP subsystem

- ARC EM processors with cache and DSP extensions deliver extremely low gate count and highly efficient processing performance

- Extensive library of software DSP functions enable sensor signal processing

- Hardware accelerators boost performance efficiency and reduce power consumption

- Integrated peripherals provide a wide range of SoC connectivity options for SoC/MCUs

- Options supporting higher performance voice/speech and sensor requirements

Product Details

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.