In a multi-tasking system, multiple processes execute on a single CPU, storing the system state for one process, so the active task can be paused and a different task can be restored and resumed. These tasks do not interfere with each other and appear to be concurrent by the means of context switches that occur in a short period of time.

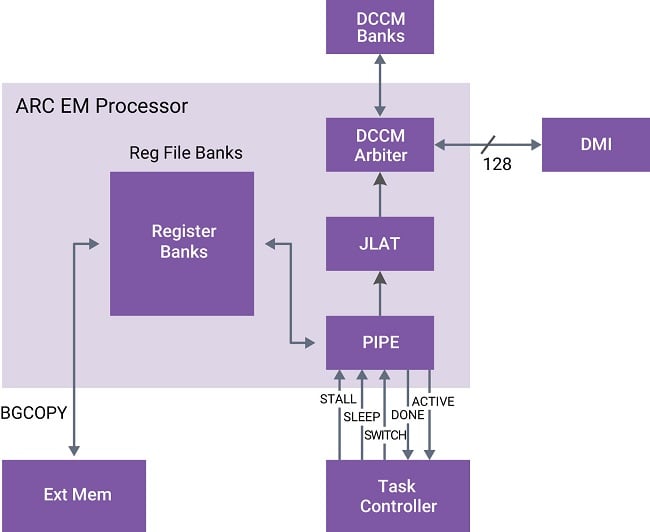

The Synopsys ARC® EM Performance Mode Option provides a coarse-grained multi-tasking architecture featuring a 4-cycle hardware context switch, which allows for higher performance in real-time, low-latency control applications while adding wider memory interface support to improve system I/O performance.

With the performance mode option enabled, the external task controller can choose any task to run next with a context switch based on the Task ID and C-based software development with no need for an RTOS.

In addition, the performance mode option also provides the ability to configure the memory interface to the closely coupled memories (CCM) with 32-, 64- or 128-bit data widths, enhancing the bandwidth and throughput of memory transactions.

ARC EM Multi-tasking Architecture

Highlights & Key Features

- Coarse grained multithreading with 4-cycle hardware context switch

- Save/Restore the context to an external memory using the background copy interface

- Control the behavior of the processor during task switching using the external task switching controller

- 32-/64-/128-bit Direct Memory Interface (DMI)

- Support for DCCM size up to 64KB

- Job Location Address Translation (JLAT) for hardware-based memory mapping

Product Details

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.