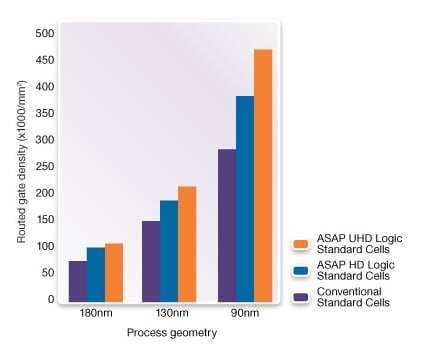

The Synopsys ASAP™ Logic Standard Cell Libraries routing methodology offers, on average, a 20% increase in area utilization. This increase in the utilization budget creates an opportunity to address different market needs.

Synopsys ASAP Logic High-Density (HD) Standard Cell Library

The Synopsys ASAP Logic HD Standard Cell Library typically yields up to 20% denser designs with better performance compared to conventional commercial libraries. As an alternative to reducing the chip size, the 20% higher routing utilization can be used to reduce the number of metal layers in a design.

Synopsys ASAP Logic Ultra-High-Density (UHD) Standard Cell Library

The Synopsys ASAP Logic UHD Standard Cell Library typically provides up to 20% smaller area when compared to conventional standard cell libraries. In addition, it consumes 20% less dynamic and up to 7X less static power power dissipation.

Synopsys ASAP Logic Ultra-Low-Power (ULP) Standard Cell Library

The Synopsys ASAP Logic ULP Standard Cell Library builds on the success of the Synopsys ASAP Logic UHD architecture by providing up to 20% smaller area when compared to conventional standard cell libraries along with more than 30X improvement in stand-by power dissipation using optional off-set biasing techniques of the unique multi-power rail architecture at 65-nm and below.

Synopsys ASAP Logic ECO Standard Cell Library

Used in conjunction with its corresponding Synopsys ASAP Logic HD, UHD or ULP Standard Cell Libraries, the Synopsys ASAP Logic (Engineering Change Order) ECO Standard Cell Library offers the best flexibility and cost-effective way to implement post-tapeout design changes by using metal programmable techniques resulting in significant savings in mask costs associated with ECO designs.

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.