The Synopsys ARC-V™ RPX-100 series processors feature a dual-issue, 64-bit superscalar architecture for use in high performance applications where performance efficiency is required. The cores offer outstanding performance delivering minimal power consumption.

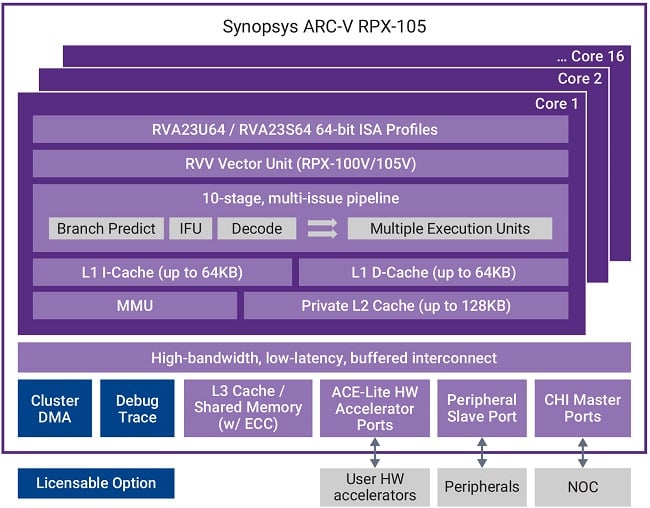

The ARC-V RPX-100 processors are based on the RISC-V instruction set architecture (ISA). The processors feature a physical address space defined by the RISC-V Sv39 MMU. For applications requiring higher performance, the multi-core RPX-105 & RPX-105V are available with up to 16 CPU cores and up to 16 hardware accelerators in the processor cluster. RISC-V vector extensions (RVV) are available in the RPX-100V (single core) and RPX-105V (multi-core) processors.

The ARC-V RPX-100 features level 1 (L1) instruction and data cache optimized for use in performance efficient applications. Each core also supports up to 128KB of private L2 cache. The multi-core cluster supports an additional 16MB of cluster shared cache (L3).

Synopsys ARC-V RPX-105 Block Diagram

![]() Synopsys ARC-V RPX-100 Series Datasheet

Synopsys ARC-V RPX-100 Series Datasheet

Highlights & Key Features

- Dual-issue, 64-bit processors for performance efficient host applications

- Multicore Processor versions with up to 16 CPU cores and up to 16 hardware accelerators

- Based on the RISC-V ISA, leveraging standard 64-bit protocols (and extensions)

- Hardware virtualization support

- Support for custom instructions

- Support for up to 64KB of L1 instruction and data cache

- Up to 128KB of unified private L2 cache per core

- Up to 16MB of shared cluster cache (L3)

- RISC-V Sv39 MMU with hardware page table walk and up to 4 MB page sizes

- Optional support for RISC-V defined vector extensions (RVV)

- Optional ARC Trace Interface support provides real-time trace debugging features

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.