The ASIL compliant Synopsys ARC® VPXxFS DSP IP is a family of VLIW/SIMD processors enabling automotive system-on-chip (SoC) designers to accelerate advanced driver assistance systems (ADAS), RADAR and LiDAR sensor processing application development and ISO26262 certification for systems using digital signal processing.

The VPXxFS Family supports multiple vector lengths and core configurations:

- 128-bit vector word – VPX2FS (single core), VPX2x2FS (dual core)

- 256-bit vector word – VPX3FS (single core), VPX3x2FS (dual core)

- 512-bit vector word – VPX5FS (single core), VPX5x2FS (dual core), VPX5x4FS (quad core)

- 1024-bit vector word – VPX6FS (single core), VPX6x2FS (dual core), VPX6x4FS (quad core)

The VPXxFS Family comes with integrated hardware safety features such as ECC protection for memories and interfaces, safety monitors and lockstep mechanisms that achieve the most stringent levels of ISO 26262 functional safety compliance.

To speed application software development, the VPXxFS Family is supported by Synopsys’ ARC MetaWare tools for Safety, which provide a comprehensive and vector-length agnostic software programming environment that enables code portability among all members of the VPXxFS family. The tool suite includes a safety-certified optimizing C/C++ vector compiler, debugger, instruction set simulator, as well as vector-based DSP, machine learning inference, linear algebra and vision processing libraries.

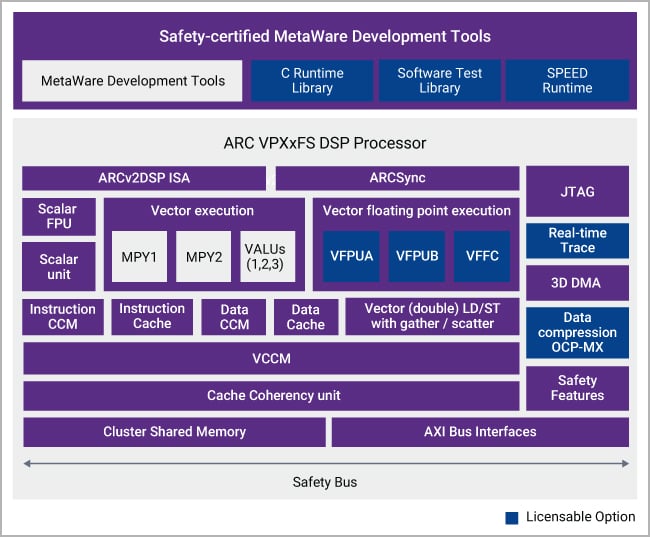

Synopsys ARC VPXxFS DSP Processor Block Diagram

Highlights & Key Features

- Integrated hardware safety features with minimal area and power impact for full ASIL compliance, certified for ASIL D systematic, up to ASIL C random

- Four-way VLIW architecture combining scalar and vector operations

- 128-bit, 256-bit, 512-bit and 1024-bit vector lengths

- 8, 16, and 32-bit integer SIMD engines

- IEEE 754-compliant vector floating point unit option offers single-precision or half precision operations and advanced math functions

- Dual vector floating point SIMD pipes

- Hardware acceleration for linear and non-linear math functions

Product Details

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.