Synopsys USB 3.1 PHY IP provides designers with the industry's best combination of low area and low power with support for the leading process technologies to 5nm. Both the USB-C 3.1 and USB 3.1 PHYs use a single efficient GDSII design that supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes. To maximize battery life in mobile applications, the Synopsys USB-C/USB 3.1 PHYs are designed to minimize power consumption and standby current. In addition, the DesignWare USB-C 3.1 femtoPHY is optimized to support the USB Type-C connectivity specification.

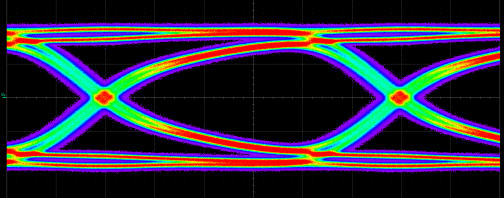

Industry’s first PHY IP to support Type-C connectivity, the DesignWare USB/USB-C 3.1 PHYs,

offer clear margins at 10 Gbps USB 3.1 throughput.

Synopsys USB IP is the most certified USB IP solution in the industry. With over 3,000 design wins and approximately three billion silicon-proven units shipped, Synopsys' complete USB IP solution, consisting of digital controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits, enables designers to lower integration risk and speed time-to-market.

Highlights & Key Features

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

- Integrated PHY includes transmitter, receiver, PLL, digital core, and ESD

- Design minimizes area and power

Product Details

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.