As part of Synopsys Foundation IP portfolio, the Synopsys Logic Library IP provides a broad portfolio of pre-designed standard-cell solutions for system-on-chip (SoC) designs, offering pre-verified, optimized building blocks (high-density, low-power) to speed up development. In addition, Synopsys Logic Library IP offer Power Optimization Kits (POKs) and Engineering Change Order (ECO) Kits that deliver outstanding performance, with low power, and small area in the advanced nodes of leading foundries.

Multiple Architectures, Multiple VTs, Multi-Channel Lengths

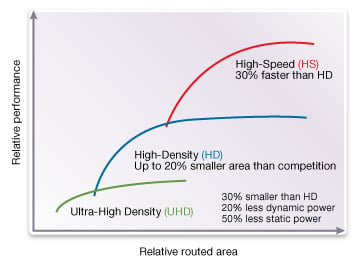

The Synopsys SiWare Logic Libraries provide three separate architectures, high-speed (HS), high-density (HD), and ultra high-density (UHD), to optimize circuits for performance, power and area tradeoffs.

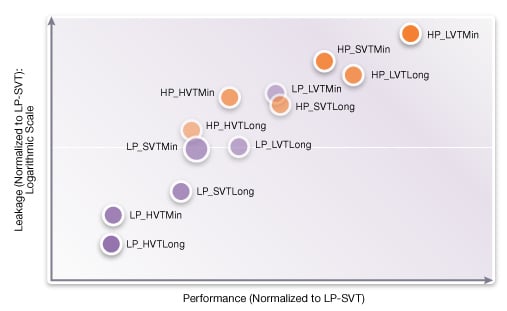

The standard cell libraries include multiple voltage threshold implants (VTs) at most processes from 180-nm to 2-nm and support multiple channel (MC) gate lengths to minimize leakage power at 40-nm and below.

Ideal for tablet, smartphone, cell phone, graphics, networking, storage, and other high-performance applications requiring low power and high density, Synopsys Logic Libraries and Memory Compilers provide a unique set of options that enable SoC designers to optimize their products for speed, area, dynamic power, standby power, and cost.

Highlights, Key Features & Datasheets

- Maximum Performance

- High-performance libraries for critical paths of GHz processors

- Close timing in fewer iterations without sacrificing area or power

- Multiple Libraries per Process Node

- Base Libraries include cell set in multiple architectures/ VTs at minimum channel length

- Multiple Channel Length Libraries (MC) for leakage reduction at 40-nm and smaller and to reduce die-to-die leakage and timing variability

- Power Optimization Kits enable shut-down and multiple voltage domains

- ECO Kits enable metal-only post-silicon fixes to cost-effectively address bugs

- High Performance Core (HPC) Design Kits offered at 40-nm and smaller with datapath cells and multi-bit flip-flops

- Metal-programmable libraries for flexible, metal-only design changes over life of product

- Ultra Low Leakage Libraries provide up to 100X leakage reduction for building always-on blocks

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.