The Synopsys SiWare™ Logic Libraries product line features yield-optimized, Design for Manufacturability (DFM)-compliant standard cells tailored for a broad range of design applications at advanced process nodes. SiWare Logic Libraries are available in three distinct architectures—High-Density (HD), Ultra-High-Density (UHD), and High-Speed (HS)—allowing designers to optimize circuits based on area, speed, and power requirements.

These libraries are ideally suited for customers in graphics, networking, storage, mobile, and other high-performance applications that demand high density and low power. Available in 65 nm, 40 nm, and 28 nm technologies, SiWare Logic Libraries provide a comprehensive set of options to help reduce die size, manage power efficiently, and achieve high performance, along with robust test and repair features. This flexibility enables customers to differentiate their products in terms of speed, area, dynamic power, standby power, and overall cost.

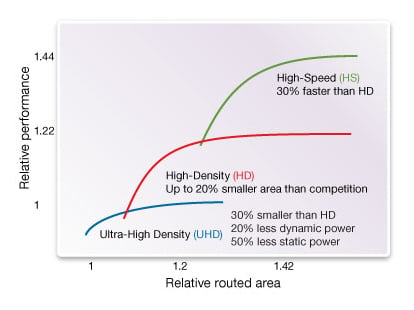

Performance vs. Area for High-Density, High-Speed and Ultra-High-Density Libraries

The Synopsys Power Optimization Kits (POKs) enable designers to minimize power consumption while maintaining optimal performance. These kits enable designers dynamic operation of functional blocks at multiple voltages, allowing for the optimal trade-offs between dynamic power consumption and performance across multiple operating modes. Key features include:

- Level shifters to support multiple voltage islands

- Power-gating for domain isolation

- Data retention flip-flops and always-on cells for fast wake-up

- Biasing cells for effective leakage control

- Pitch matched compatibility with High-Density, High-Speed and, Ultra-High-Density cells

- Availability in multiple thresholds

- Support for industry-standard EDA power flows

In addition, the Synopsys ECO Extension Library Kits provide designers with the flexibility to implement logic changes using metal-only modifications for cost-effective bug fixes. These kits can be utilized post place-and-route to address last minute product requirements or resolve final verification issues, offering:

- Base array filler cells

- Metal-programmable macros

- Combinational, sequential, and support cells

- Multiple drive strengths

- Empty sites can be filled with DCAP cells

Highlights & Features

- DFM compliant for high yield

- Poly M2 alignment with restricted design rules (RDR) minimum area

- Standard, High and Low thresholds for power/performance trade-offs

- Low voltage corners for dynamic power saving

- Temperature inversion corners for timing accuracy

- Industry standard EDA flow support (CCS, ECSM)

- Power Optimization Kit

- Engineering Change Order (ECO) Kit

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.