The Synopsys Engineering Change Order (ECO) extension library kits provide designers with the flexibility to implement logic modifications using metal-only changes, allowing for cost-effective updates late in the design cycle. These kits are especially valuable after chip placement and routing, enabling designers to accommodate last-minute product requirements or resolve final verification issues efficiently.

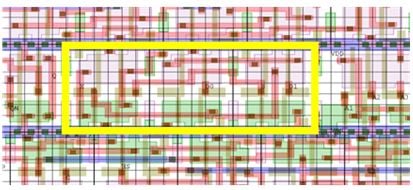

With SiWare Logic Libraries, empty ECO sites can be populated using fill cells or decoupling capacitors (DCAPs) from either the base library or the ECO Kit, depending on project needs. The ECO Kit offers characterized cells that can replace randomly placed filler or DCAP cells, providing more precise and effective logic updates. These cells can be clustered in dedicated row or column areas and are characterized with the same VTs and PVTs as the base libraries, ensuring consistency across the design.

The Synopsys ECO extension approach is easy to use and fits seamlessly into standard design flows, offering greater flexibility than traditional spare gates. Since only metal and contact layers are utilized, wafers held at contact can be finished quickly, supporting a fast time to market. The rich cell set includes base array filler cells, pre-characterized metal programmable macros, and a variety of combinational, sequential, and support cells with multiple drive strengths to meet diverse performance requirements.

Highlights & Features

- Easy to Use

- Standard design flow

- More flexible than spare gates

- Characterized cells replace randomly placed filler cells or DCAP cells

- Can be clustered in special row or column areas

- Characterized with same VTs, PVTs as base libraries

- Combinatorial (and bubble versions)

- Inverter, buffer

- Simple gates - NAND, OR

- Complex gates - NOR, XNOR

- AOI/OAI

- Mux/demux

- Sequential (and scan versions)

- Flip-flops - with clear and preset

- Scan flip-flops

- D-Type transparent latch

- Support cells

- Filler cells with and without DCAPs

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.