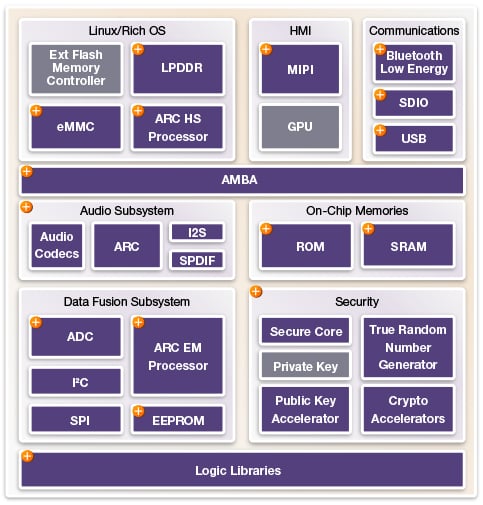

用于智能家居应用的 DesignWare IP

概述

可穿戴设备通过增强眼镜、鞋子和手表等提供实时反馈的物品的功能,将技术融入日常生活。这些设备将在扩展互联世界的过程中发挥重要作用,但设计集成在这些设备中的 SoC 会面临重大挑战,例如如何延长电池寿命、如何更大程度缩小面积和改善传感组件(即触摸、语音、音频和视频)。

高效的数据处理将成为这些解决方案的核心,而 Synopsys 种类广泛的 DesignWare®IP 产品组合经过优化,能够攻克这些 SoC 设计挑战。

悬停或点击鼠标以了解有关 DesignWare IP 解决方案的更多信息:

低功耗蓝牙

- 链路层和 PHY

- 运行电压低于一伏特

- 集成安全功能

- 支持最新的蓝牙低功耗标准

- 了解更多 >>

安全

- 加密芯核,公钥加速器,随机数产生器

- 安全协议加速器和协同处理器

- 嵌入式安全 IP 模块建立安全的硬件信任根环境

- 安全启动和加密中间件

- 了解更多 >>

音频子系统

- 小巧的低功耗 AS211SFX 处理器,用于音频 DSP

- 双核 AS221BD,用于增强型音频和多声道 HD

- SoundWave 音频子系统集成了音频硬件、软件和接口

- 种类广泛的认证音频编解码器产品组合

- 了解更多 >>

USB

- USB femtoPHY 将面积削减 50%,达到 0.16mm2

- 能够快速集成的成熟 USB 控制器

- 支持 USB 充电检测功能

- 支持电源门控和超低待机电流

- 了解更多 >>

LPDDR

- DDR PHY 编译器优化 DDR IP 配置

- 支持自动禁用缓冲器、接收器和驱动器以降低功耗

- 支持 x16 和 x32 SDRAM

- 了解更多 >>

ARC HS 处理器

- ARC HS 高性能 32 位处理器

- >3100 DMIPS@ 1.6 GHz,60mW 功率,0.15mm2 面积

- 集成用户硬件加速器的定制指令

- 了解更多 >>

SDIO

- 符合最新 SD、SDIO 和 eMMC 规范

- SD/eMMC 支持 1 位、4 位和 8 位的卡

- 低功耗选项配备时钟和电源开关功能

- 了解更多 >>

eMMC

- 符合 SD 4.1、SDIO 4.1 和 eMMC 5.1 规范

- SD/eMMC 支持 1 位、4 位和 8 位的卡

- 低功耗选项配备时钟和电源开关功能

- 了解更多 >>

SRAM

- 具有省电模式的高密度低漏电存储器

- 超低电压运行

- 深度睡眠模式可将漏电减少 70%

- 长通道器件可减少有源漏电

- 了解更多 >>

ROM

- 超低功耗防签名 ROM

- 漏电减少幅度高达 20%

- 了解更多 >>

逻辑库

- 厚氧化层“常开”逻辑库可节省静态功耗

- 多位触发器可节省动态功耗和面积

- 功耗优化套件可最大程度减少芯核漏电

- 超低电压运行(比 Vddnom 低 40%)

- 了解更多 >>

MIPI

- 可互操作的 DSI 和 CSI-2 控制器

- 功耗优化的 D-PHY

- 低功耗 Gear3 M-PHY

- 符合标准规范

- 了解更多 >>

ADC

- 高达 14 位的分辨率和高达 5 Msps 转换率

- 12 位模式下 160 µA / MSPS

- 多种电源休眠模式 (<0.05 µA)

- 紧凑的面积:~0.12 mm2 (55 nm)

- 了解更多 >>

ARC EM 处理器

- 超低功耗小型 32 位处理器

- 性能效率高达 1.81 DMIPS/MHz

- 极低的面积和功耗

- 极高的可配置性和可扩展性

- 了解更多 >>

EEPROM

- 依靠单核电压电源运行

- >10,000 次擦写次数

- 集成错误检查和纠正(ECC)功能

- 用于存储用户配置、校准和安全数据

- 了解更多 >>

AMBA

- 与 AMBA 2.0、AMBA 3 AXI、AMBA 4 AXI 和 ACE-Lite 兼容

- 了解更多 >>

亮点:

- 厚氧化层"常开"逻辑库让处于睡眠状态的常开唤醒电路实现超低漏电。

- 超高密度逻辑库提供低至 60% VddNom 的低电压支持

- 多位触发器可更大程度减少时钟负载、面积和漏电,从而改善动态和静态功耗

- DesignWare 逻辑库的功耗优化套件(POK)可实现低功耗,同时仍能保持理想性能

- 具有高级功耗管理功能的存储器编译器通过具有 0.9 V 运行电压的单引脚控制,可将漏电降低 70% 之多

- 超低功耗防签名通过 ROM 减少多达 20% 的漏电

- ARC HS 处理器实现了超大性能效率(DMIPS/mW 和 DMIPS/mm2),非常适合需要高速数据和信号处理的嵌入式应用

- 利用 ARC HS 处理器可配置和可扩展的指令集,能够根据各种实际情况进行定制,以在性能、功耗和面积上实现理想平衡

- 可编程和可配置的视觉处理器将软件解决方案的灵活性与专用硬件的低成本和低功耗相结合,同时加入了实现卷积神经网络的对象检测引擎

- 传感器和控制器 IP 子系统通过紧密结合的存储器和传感器接口外设以及硬件加速器,提高性能并减少代码大小,从而显著节省面积并降低延迟

- DDR multiPHY IP 与 DesignWare Universal DDR 数字控制器和验证 IP 相结合,可提供完整的多协议 DDR 接口 IP 解决方案,支持 LPDDR2/3

- MIPI CSI-2 和 DSI 控制器符合第 1.2 版规范。分别支持 1 到 8 和 1 到 4 个数据通道,D-PHY PPI 接口每通道工作速率高达 2.5 Gbps

- 具有高达 14 位分辨率和 5 Msps 转换速率的 ADC 超越了领先的片上实施技术

- 获得认证的成熟 USB 2.0 控制器和 PHY 极易集成并支持低功耗电池充电功能

- 紧凑型蓝牙低功耗链路层和 PHY 可实现安全的无线连接,扩展了覆盖范围且降低了功耗,可延长电池寿命,适用于可穿戴设备和智能家居应用

- 安全 IP 包括公钥加速器、真随机数生成器和安全协议加速器以及安全硬件信任根,可防御不断演变的威胁

- SD / eMMC 控制器 IP 通过命令排队引擎为 SD、SDIO 和 eMMC 提供高级功能