Synopsys IP Technical Bulletin Article

Connecting a Standard SRAM Device to an AMBA 3 AXI Subsystem Using the DesignWare Generic Slave

Introduction When adding an SRAM to an AMBA 3 AXI-based system, figuring out how to interface the SRAM to the bus can be a challenge. Many of the available off-the-shelf memory controllers are not specifically designed to control SRAM devices and include logic for controlling SDRAM, Flash, and other devices that require more control logic than that required by an SRAM device. This all adds to the overhead associated with off-the-shelf solutions. Not only that, the memory controllers that support SRAM devices typically have a built- in AMBA2 interface that requires extra bridging logic to interface to AXI. The extra logic for controlling other memory types causes the controllers to take up a large amount of chip area, typically more than 20k gates. This is complicated by the fact that bridges consume extra area, as well. Lastly, not only do the bridges consume area, they introduce latency. With off-the-shelf memory controllers being less than a perfect option, the only alternative would seem to be to write a custom AMBA 3 AXI-based interface for the standard SRAM device. Fortunately, there is another option. The DesignWare Generic Slave (DW_axi_gs) can be used as the interface for the SRAM while consuming less than 4k gates. This application note discusses an example of connecting a standard SRAM module to an AXI subsystem using the DW_axi_gs. The following discussion shows what is needed to interface the Generic Interface (GIF) signals on the DW_axi_gs to the SRAM interface signals. Generic Slave Interface - DW_axi_gs The Generic Interface Module for AMBA AXI Slave, DW_axi_gs, simplifies the connection of custom or third-party slave components-such as a standard SRAM device-to the AMBA AXI bus using a Generic Interface (GIF). The GIF consists of two independent channels for requests and responses. Each channel is a point-to-point connection from a single source to a single sink. The channels offer two-way flow control similar to the valid/ready handshake on the AXI bus. The DW_axi_gs provides a configuration option, GIF Lite mode, which allows for simple function GIF slaves to be connected to DW_axi_gs. The standard SRAM device is the kind of device for which this mode was intended. Requirements of the SRAM for the DW_axi_gs to be configured in Gif Lite mode are:By Fred Roberts, CAE

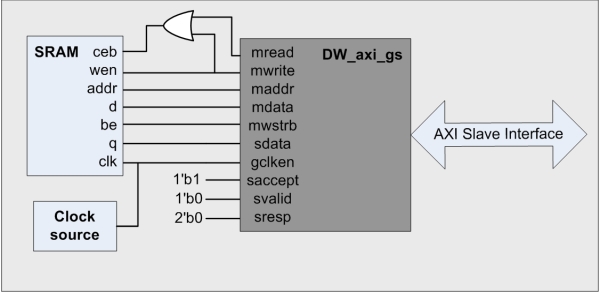

Figure 1. DW_axi_gs and SRAM singal connections GS_GIF_LITE=1

| SRAM Signal list | |

| • clk | sram clock |

| • wen | sram write enable |

| • ceb | sram chip enable |

| • addr | sram address bus |

| • d | sram write data |

| • be | sram byte enable |

| • q | sram read data |

| DW_axi_gs Signal List | |

| • gclken | GS clock enable |

| • maddr | GS address output |

| • mread | GS read enable output |

| • mwrite | GS write enable output |

| • mdata | GS write data output |

| • mwstrb | GS byte strobe output |

| • sdata | GS read data input |

Below is an example instantiation of a standard SRAM device and the DW_axi_gs. It shows the directly connected signals and the signals that are tied to a static value. It also shows the logic needed to generate the chip enable for the SRAM device, which is an OR of the mread and mwrite signals from the DW_axi_gs.

SRAM U_SRAM ( .clk (gclk) // sram clock .wen (gs_mwrite) // sram write enable .ceb (w_chip_enable) // sram chip enable .addr (w_maddr) // sram address bus .d (gs_mdata) // sram write data .be (gs_mwstrb) // sram byte enable .q (gs_sdata) // sram read data ); assign w_chip_enable = gs_mread | gs_mwrite; DW_axi_gs U_DW_axi_gs ( .gclken (gclk) // GS clock enable .maddr (gs_maddr) // GS address output .mread (gs_mread) // GS read enable output .mwrite (gs_mwrite) // GS write enable output .mburst () // GS burst output .mlen () // GS burst length output .msize () // GS transfer size output .mlast () // GS last output .mdata (gs_mdata) // GS write data output .mwstrb (gs_mwstrb) // GS byte strobe output .saccept (1.b1) // GS slave accept input .svalid (1.b0) // GS response valid input .sdata (gs_sdata) // GS read data input .sresp (2.b0) // GS response input .mready () // GS ready for response output );The above instantiations, when combined with setting the GS_GIF_LITE parameter to true, are all that is needed to attach a standard SRAM to the DW_axi_gs. Since there will never be an error response, sresp is driven to 0 so that the DW_axi_gs always sends an auto-generated OKAY or EXOKAY response on the AXI bus. Additionally, there will never be a flow control event, so two-way flow control is disabled. The saccept input to DW_axi_gs is driven high, and DW_axi_gs always drives the mready output high. Reference Documentation All of the following documents can be found in the Guide to DesignWare AMBA IP Components Documentation. After installing the DesignWare Synthesizable IP for AMBA, this document can also be found on your local system at $DESIGNWARE_HOME/doc/amba/latest/intro.pdf.

- DW_axi_gs Databook and Release Notes - For detailed information on the configuration and usage of the DW_axi_gs.

- DW_axi Databook and Release Notes - Provides details of the DesignWare Interconnect Fabric for AMBA 3 AXI.

Search Tools