Synopsys ARC HS56, HS57D, and HS58 Processors

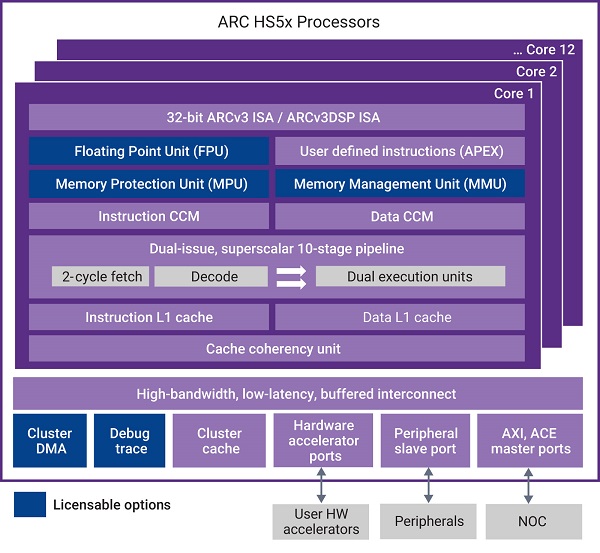

The Synopsys ARC® HS56, HS57D and HS58 processors feature a dual-issue, 32-bit superscalar architecture for use in embedded applications where performance and high clock speed are required. The cores can be clocked at up to 1.8 GHz in 16FFC processes (worst case, single core, base configuration) and offer outstanding performance delivering 3.0 DMIPS/MHz and 6.16 CoreMark/ MHz with a small area footprint and low power consumption.

The ARC HS56, HS57D and HS58 processors are based on the advanced ARCv3 instruction set architecture (ISA) and pipeline, which provides leadership power efficiency and code density. For applications requiring higher performance, Multicore Processor (MP) versions of the HS56, HS57D and HS58 are available with support for up to 12 HS CPU cores and up to 16 hardware accelerators in the processor cluster.

The ARC HS56 and HS57D feature level 1 (L1) instruction and data cache and closely coupled memory (CCM) and are optimized for use in high-performance real-time embedded applications. The HS58 is designed for use in applications running Linux or SMP Linux. The HS58 has all the features of the HS56 plus support for L2 cache up to 64 MB and a Memory Management Unit (MMU).

The HS56, HS57D and HS58 are designed to be used in applications such as SSD controllers, networking, wireless modems, automotive systems, smart appliances, and other high-end embedded applications.

To maximize PPA of ARC HS5x Processor-based designs, a Fusion QuickStart Implementation Kit (QIK) that includes tool scripts, a baseline floorplan, design constraints and documentation, is available.

Synopsys ARC HS56, HS57D, and HS58 Block Diagram

![]() Synopsys ARC HS56, HS57D, and HS58 Processors Datasheet

Synopsys ARC HS56, HS57D, and HS58 Processors Datasheet

- Dual-issue, 32-bit processors for high-performance embedded applications

- Deliver up to 5400 DMIPS and 11,088 CoreMark per core at 1.8 GHz on 16FFC (worst case conditions, single-core configuration)

- Multicore Processor versions with up to 12 CPU cores and up to 16 hardware accelerators

- Based on advanced ARCv3 ISA

- High degree of configurability

- Enhanced MMU (HS58) with hardware page table walk and 40-bit physical address space

- Support for ARCv3DSP that adds 150 DSP instructions (HS57D)

- Support for APEX custom instructions

- Support for up to 16 MB of closely coupled memory and direct mapping of peripherals

- Floating Point Unit (FPU) supporting half, single- and double-precision IEEE 754-compliant operation

- ARC Trace Interface provides real-time trace debugging features

- Fusion QuickStart Implementation Kit (QIK) with tool scripts, a baseline floorplan, design constraints and documentation maximizes PPA

| ARC HS56MP multi-core version of dual-issue HS56 with I and D cache for high-performance embedded applications | STARs | Subscribe |

| ARC HS56 32-bit, dual-issue processor core & interconnect, ARCv3 ISA, for embedded applications | STARs | Subscribe |

| ARC HS57DMP multi-core version of dual-issue HS57D ARCv3DSP ISA, with I&D cache | STARs | Subscribe |

| ARC HS57D 32-bit, dual-issue processor core and interconnect, ARCv3DSP ISA, with I&D cache | STARs | Subscribe |

| ARC HS58MP multi-core version of dual-issue HS58 processor w/ MMU, ARCv3 ISA, for embedded Linux applications | STARs | Subscribe |

| ARC HS58 32-bit, dual-issue processor with MMU, interconnect, ARCv3 ISA, for embedded Linux applications | STARs | Subscribe |

| Description: | ARC HS56 32-bit, dual-issue processor core & interconnect, ARCv3 ISA, for embedded applications |

| Name: | dwc_arc_hs56_core |

| Version: | 1.00a |

| ECCN: | 3E991/NLR |

| STARs: | Open and/or Closed STARs |

| myDesignWare: | Subscribe for Notifications |

| Product Type: | DesignWare Cores |

| Documentation: | |

| Download: | arc_v3_hs_processor |

| Product Code: | F715-0 |

| Description: | ARC HS56MP multi-core version of dual-issue HS56 with I and D cache for high-performance embedded applications |

| Name: | dwc_arc_hs56mp_core |

| Version: | 1.00a |

| ECCN: | 3E991/NLR |

| STARs: | Open and/or Closed STARs |

| myDesignWare: | Subscribe for Notifications |

| Product Type: | DesignWare Cores |

| Documentation: | |

| Download: | arc_v3_hs_processor |

| Product Code: | F735-0 |

| Description: | ARC HS57D 32-bit, dual-issue processor core and interconnect, ARCv3DSP ISA, with I&D cache |

| Name: | dwc_arc_hs57d_core |

| Version: | 1.00a |

| ECCN: | 3E991/NLR |

| STARs: | Open and/or Closed STARs |

| myDesignWare: | Subscribe for Notifications |

| Product Type: | DesignWare Cores |

| Documentation: | |

| Download: | arc_v3_hs_processor |

| Product Code: | F736-0 |

| Description: | ARC HS57DMP multi-core version of dual-issue HS57D ARCv3DSP ISA, with I&D cache |

| Name: | dwc_arc_hs57dmp_core |

| Version: | 1.00a |

| ECCN: | 3E991/NLR |

| STARs: | Open and/or Closed STARs |

| myDesignWare: | Subscribe for Notifications |

| Product Type: | DesignWare Cores |

| Documentation: | |

| Download: | arc_v3_hs_processor |

| Product Code: | F737-0 |

| Description: | ARC HS58 32-bit, dual-issue processor with MMU, interconnect, ARCv3 ISA, for embedded Linux applications |

| Name: | dwc_arc_hs58_core |

| Version: | 1.00a |

| ECCN: | 3E991/NLR |

| STARs: | Open and/or Closed STARs |

| myDesignWare: | Subscribe for Notifications |

| Product Type: | DesignWare Cores |

| Documentation: | |

| Download: | arc_v3_hs_processor |

| Product Code: | F738-0 |

| Description: | ARC HS58MP multi-core version of dual-issue HS58 processor w/ MMU, ARCv3 ISA, for embedded Linux applications |

| Name: | dwc_arc_hs58mp_core |

| Version: | 1.00a |

| ECCN: | 3E991/NLR |

| STARs: | Open and/or Closed STARs |

| myDesignWare: | Subscribe for Notifications |

| Product Type: | DesignWare Cores |

| Documentation: | |

| Download: | arc_v3_hs_processor |

| Product Code: | F714-0 |