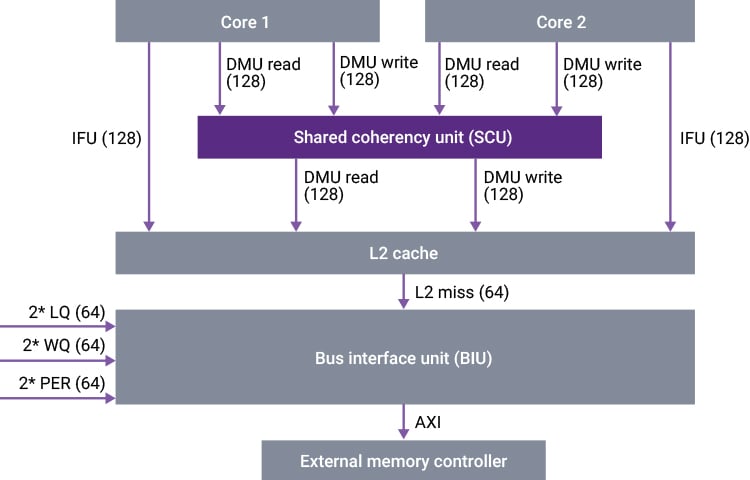

The ARC HS38 and HS48 have support for up to 8 MB of L2 cache and it is available as a separately licensed option for the HS36, HS46 and HS47D. The L2 cache is user configurable from 128KB to 8 MB and can be used with a single-core or multi-core implementation with all CPUs in a multicore cluster sharing the same L2 cache. This cache is designed to run at the same clock frequency as the CPU core and can be configured for 4, 8, 16 or 32 memory banks. The coherent L1 caches will work in concert with the L2 cache and the L2 cache is tightly connected to the core(s) through a proprietary low latency bus. The L2 cache interface to the AXI subsystem is configurable to either 64 or 128 bits wide. These features ensure that the L2 cache can support the bandwidth needed by the CPUs while avoiding AXI bus traffic on the datapaths between the CPU cores and the L2 cache.

The L2 cache connects seamlessly to HS cores and provides up to 16 ports to connect to the cores and hardware accelerators in the cluster. Requests from ports are independently executed unless there is a data dependency. The L2 is configurable and can be implemented with high-density SRAM to lower power consumption. The replacement algorithm is LRU with configurable tag banks to enable the best performance and efficient implementation. The L2 cache has user configurable support for parity, ECC and optional BIST hardware. L2 cache sees two types of errors: ECC or parity errors and memory bus errors. The L2 cache support several clock gating and power down modes that they user can use to control power consumption

Highlights & Key Features

- L2 cache configurable from 128K to 8MB

- Connects seamlessly to the L1 cache and system coherency unit

- Configurable to provide the optimal solution

- Can be used with single or multicore clusters

- Supports up to sixteen input ports

- Port waylock registers enable portioning between cores in a cluster

- LRU replacement algorithm with configurable tag banks to enable the best performance

- Cache line size: 64B, 128B

- Cache ways: 4, 8, 16

- Number of tag banks: 4, 8, 16, 32

- Number of data banks: 4, 8, 16, 32

- Support for clock gating and lower power modes

- Optional parity, ECC, or BIST

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.