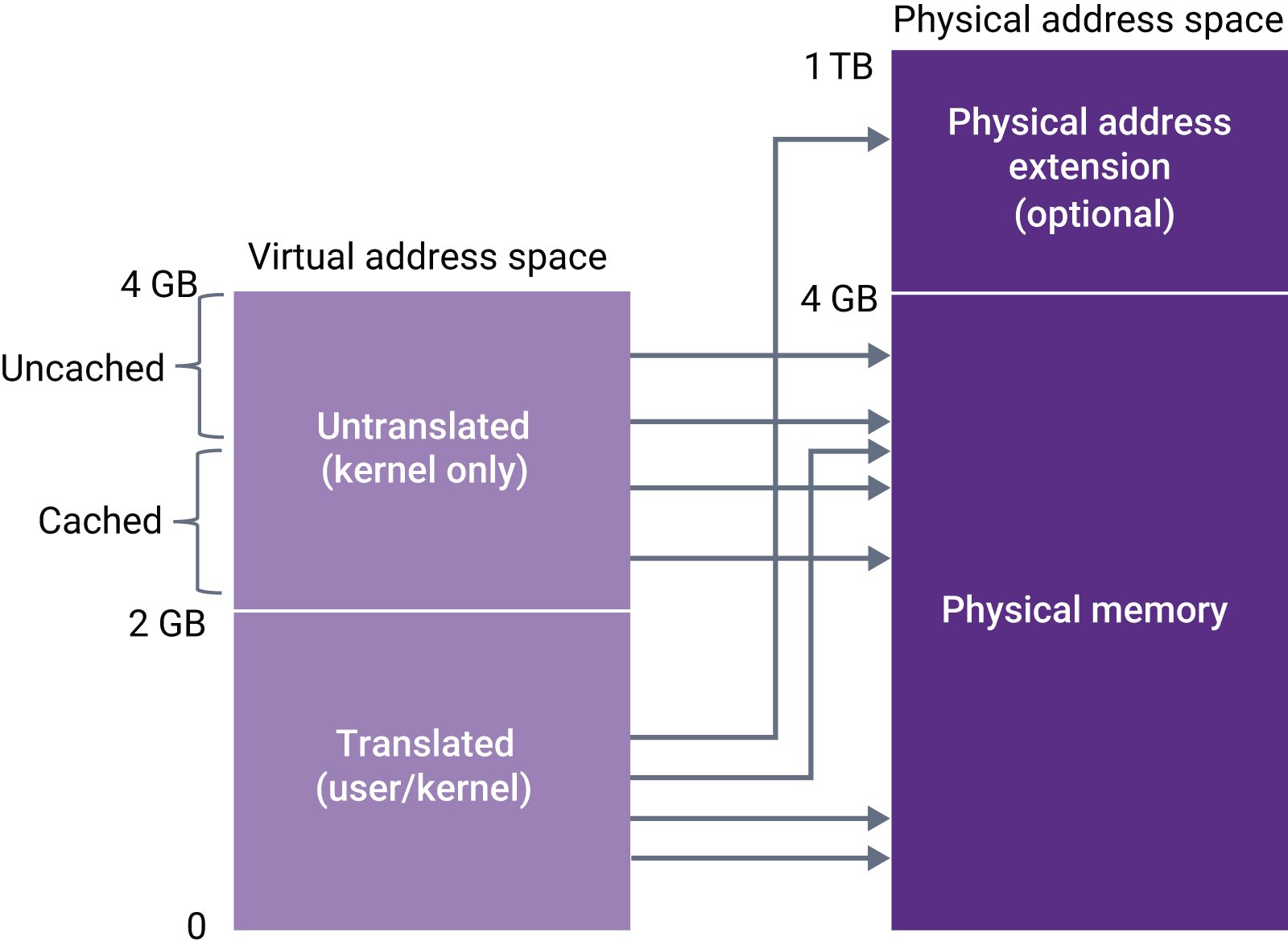

The ARC HS MMU is included with the HS38 and HS48 products and can be separately licensed as an option for use with the HS36, HS46 and HS47D products. The ARC HS MMU enables the core to run sophisticated embedded operating systems that support both Symmetric Multiprocessing (SMP) and virtual memory providing hardware support and acceleration for address translation and protection. The MMU has a configurable physical address space up to 40 bits, enough for directly addressing up to one terabyte of memory.

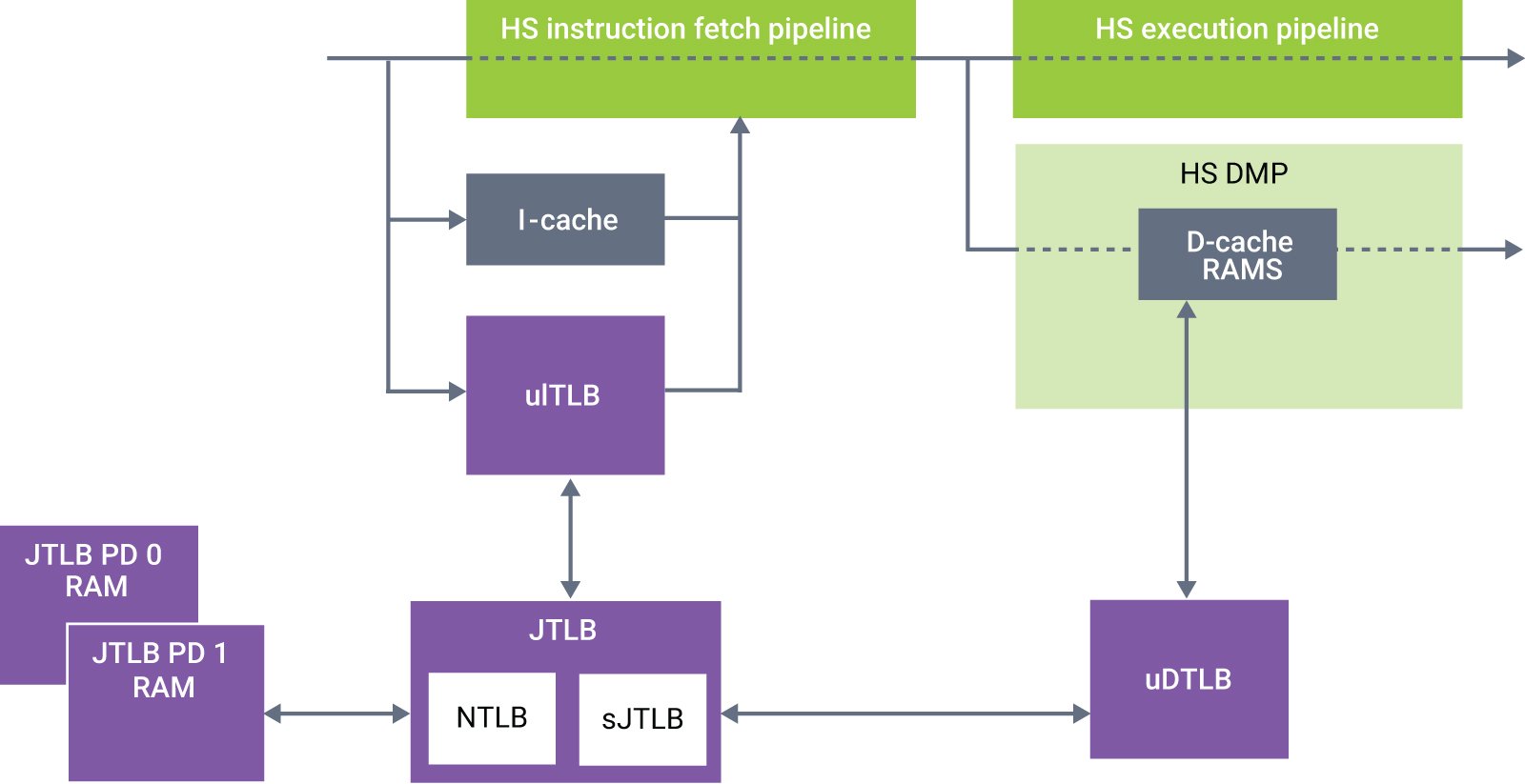

The MMU supports variable page sizes and can concurrently support memory pages in the normal range (up to 16 KB) as well as large pages (up to 16 MB). The primary Translation Lookaside Buffer (TLB) on the HS48 MMU has 1,024 entries and is four-way set associative. The TLB has fully associative micro-TLBs: a four-entry iTLB for instructions and an eight-entry dTLB for data. There is also a 16 entry secondary TLB for super/large pages. The MMU supports software managed page table walking.

ARC HS MMU Structure

Error detection and correction (ECC) in the NTLB PD0 (tag) and PD1 (data) RAMs using a SECDED code are supported in the ARC HS MMU.

Highlights & Key Features

- Common address space for kernel and user modes

- Two configurable concurrent page sizes – normal (4KB-16KB), large (2MB–16MB)

- Configurable physical address extension up to 40-bits (1TB)

- Configurable joint TLB depth of 256, 512, or 1K entries (four-way set associative)

- Joint TLB optionally includes 16-entry Super-page TLB

- Unified address space for instructions and data

- Virtually indexed physically tagged instruction cache

- Physically indexed physically tagged data cache using cache color prediction

- Software managed page table walking

- Eight-bit address space identifier (ASID)

- Shared library ASID option with support for 64 shared pages of any available size

- Separate read/write/execute flags for kernel and user modes

- Cache and memory system controls

- Global access control

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.