Full Performance Digital Signal Processing for ARCv1 Processors

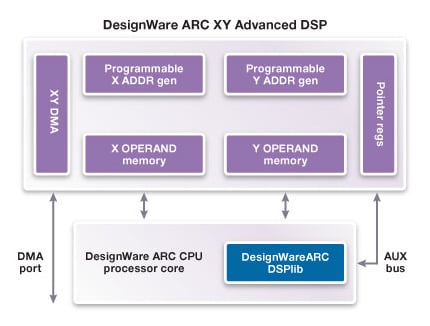

Synopsys' ARC® XY option gives designers the ability to add the power of a true DSP engine to ARCv1 CPU cores, enabling conventional and signal processing computation within a single unified architecture. The ARC XY option may be applied to most of the cores within the ARC 600 and ARC 700 families.

Synopsys also offers DSPlib, a library of frequently used signal processing functions that have been verified and optimized for the ARC XY option. The library takes full advantage of Synopsys' configurable architecture to maximize the performance of each function.

ARCv1 cores with the ARC XY option provide a complete solution for many complex computation problems in system-on-chips (SoCs) that are targeted at communications, media processing and many other applications.

XY Memory Architecture

The ARC XY architecture is built around two memory structures, X and Y, which source two operands and receive results in the same cycle.

Data in the XY memory is indexed via pointers from address generators and supplied to the ARC CPU pipeline for processing by any ARC instruction. The memories are software-programmable to provide 32-bit, 16-bit, or dual 16-bit data to the pipeline.

Additionally, an internal DMA engine moves data in and out of XY memory without impacting the processor pipeline.

Note: The XY memory functionality is available as an option for ARCv1 processors (ARC600, and ARC700 families). Similar functionality is also natively supported by some ARCv2 processors – specifically, the ARC EM9D and EM11D processors.

Memory Configuration Options

| Synopsys ARC XY with 600 Family Core | Synopsys ARC XY with 700 Family Core |

|---|---|

| Single or dual port | Dual port |

| 1 or 2 banks | 1 bank |

| 1 KB - 32 KB per bank | 8 KB - 64 KB |

Address Generator Facilities

The ARC XY option address generators make complex address calculations independently, removing a significant overhead from the CPU.

The address generators operate in several addressing modes under software control to optimize performance on DSP algorithms:

- Variable offset

- Modulo

- Bit reverse

The address may either be updated after access or remain unchanged depending on the instruction.

ARC DSPlib

The ARC DSPlib is a library of instruction extensions developed and verified by Synopsys to accelerate common DSP processing algorithms. This library allows any of these instructions to be applied to an ARC core with the ARC XY option by a simple drag and drop in the Synopsys ARChitect Processor Configurator tool. Example ARC DSPlib extensions include:

- Dual FFT

- Viterbi

- CRC

- 24 x 24 MAC

Highlights & Key Features

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.