Synopsys 224G Ethernet PHY IP Documentation and Downloads

2024-01-09 07:58:47

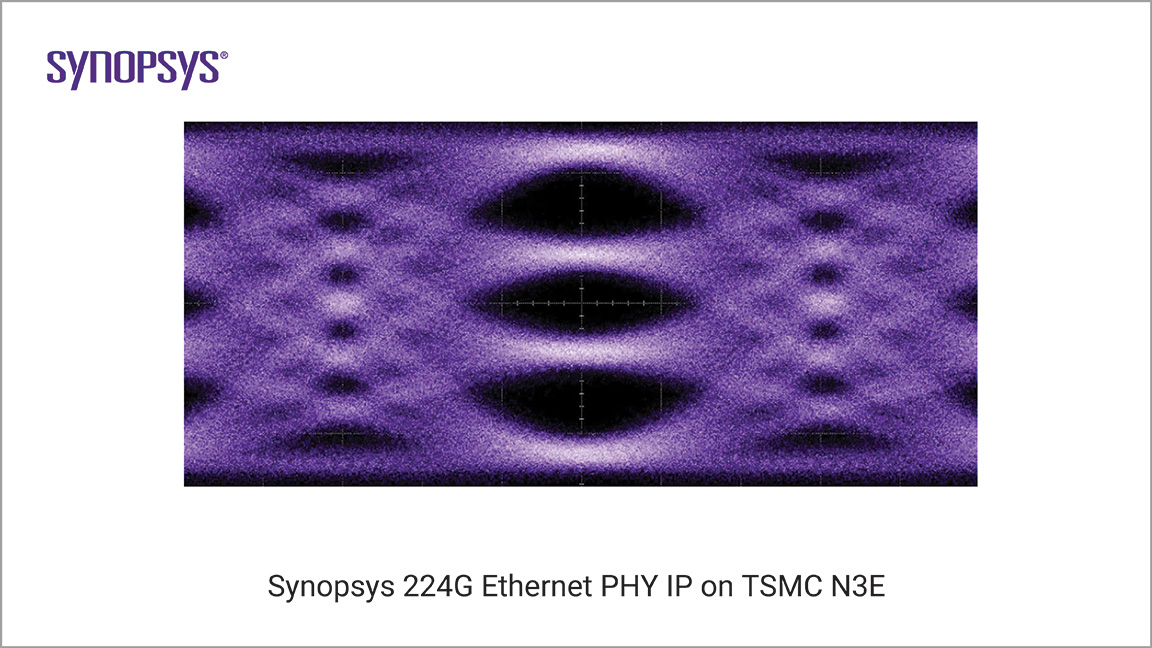

The Synopsys 224G Ethernet PHY IP, an integral part of Synopsys’ high-speed SerDes IP portfolio, meets the growing high bandwidth and low latency needs of high-performance data center applications. Using leading-edge design, analysis, simulation, and measurement techniques, the Synopsys 224G Ethernet PHY delivers exceptional signal integrity and jitter performance that exceeds the IEEE 802.3 and OIF standards electrical specifications.

The area efficient PHY demonstrates zero post-FEC BER with ultra-high power efficiency for upcoming OSFP and OSFP -XD form factors. The 1.25-224Gbps PHY supports Pulse-Amplitude Modulation 4 and Non-Return-to-Zero (NRZ) signaling to deliver up to 1.6T Ethernet in an eight lane configuration.

The configurable transmitter and advanced DSP-based receiver with analog-to-digital converter (ADC) enable designers to control and optimize signal integrity and performance. The CCA algorithm provides a robust performance across voltage and temperature variations. The low jitter PLLs and multi-loop clock and data recovery circuits provide robust timing recovery and better jitter performance, while the embedded bit error rate (BER) tester and internal eye monitor provide on-chip testability and visibility into channel performance.

The PHY integrates with the Synopsys Physical Coding Sublayer and Digital Controllers/Media Access Controller (MAC) IP solutions to reduce design time and to help designers achieve first-pass silicon success.

Combined with Synopsys’ routing feasibility study, packages substrate guidelines, signal and power integrity models, and thorough crosstalk analysis, Synopsys provides a comprehensive 224G Ethernet PHY solution for fast and reliable SoC integration.

Highlights

Products

Downloads and Documentation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

- Meets the performance requirements of chip-to-chip, chip-to-module, and long reach copper/ backplane interconnects

- DAC-based PAM-4 transmitter includes feed-forward equalization (FFE)

- Digital-based receiver consists of analog front-end (AFE), ADC, and advanced digital signal processor (DSP)

- High-performance receiver equalization supports channel loss of 45dB

- Continuous calibration and adaptation (CCA) provides robust performance across voltage, and temperature

- Low jitter phase-locked loops (PLLs) provide robust timing recovery and better jitter performance

| Description: | 224G Ethernet PHY, Intel 18A x4, North/South (vertical) poly orientation |

| Name: | dwc_224g_ethernet_phy_in18a_x4ns |

| ECCN: | 5E991/NLR |

| STARs: | Open and/or Closed STARs |

| myDesignWare: | Subscribe for Notifications |

| Product Type: | DesignWare Cores |

| Documentation: | Contact Us for More Information |

| Description: | 224G Ethernet PHY, TSMC N3E x4, North/South (vertical) poly orientation |

| Name: | dwc_224g_ethernet_phy_tsmc3eff_x4ns |

| ECCN: | 5E991/NLR |

| STARs: | Open and/or Closed STARs |

| myDesignWare: | Subscribe for Notifications |

| Product Type: | DesignWare Cores |

| Documentation: | Contact Us for More Information |

Search Tools