Advanced graphics, high-performance computing (HPC) and networking applications are requiring more memory bandwidth to keep pace with the increasing compute performance brought by advanced process technologies. With the Synopsys HBM2/HBM2E IP solution, designers can achieve their memory throughput requirements with minimal power consumption and low latency.

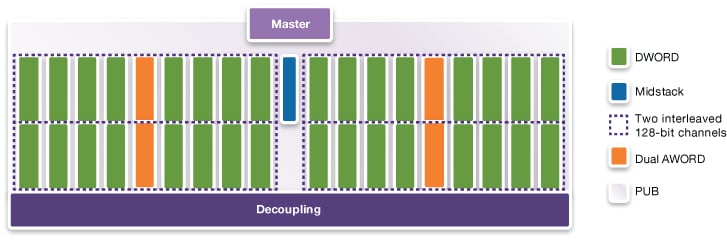

The complete Synopsys HBM2/HBM2E IP solution includes controller, PHY and verification IP, enabling designers to achieve up to 460 GBps aggregate bandwidth, which is over 14 times the bandwidth of a 72-bit DDR4 interface operating at up to 3200 Mbps. In addition, the Synopsys HBM2/HBM2E IP solution delivers approximately 10X better energy efficiency than DDR4. The Synopsys HBM2/HBM2E IP solution leverages elements from Synopsys’ silicon-proven DDR4 IP, which has been validated in hundreds of designs and shipped in millions of systems-on-chips (SoCs), enabling designers to lower integration risk and accelerate adoption of the new standard. In addition, Synopsys HBM IP is in volume production with numerous customer SoCs. The Synopsys HBM2/HBM2E PHY is provided as a set of hard macrocells delivered as GDSII along with a soft PHY Utility Block (PUB). The hard macrocells include integrated application-specific HBM2/HBM2E I/Os required for HBM2/HBM2E signaling and are easily assembled into a complete 512- or 1,024-bit HBM2/HBM2E PHY. The PUB provides the PHY configuration registers, training algorithms, and BIST features of the interface. The design is optimized for high performance, low latency, low area, low power, and ease of integration.

Figure 1: Synopsys HBM2/HBM2E PHY IP Block Diagram

In select process technologies, Synopsys also offers pre-hardened HBM2/HBM2E PHY options. For designers with unique requirements, Synopsys also offers services to harden a DDR/HBM PHY to meet exact target requirements including metal stack, decoupling parameters, etc.

Highlights & Key Features

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

- Up to 2400 Mbps with HBM2

- Up to 3600 Mbps with HBM2E

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.