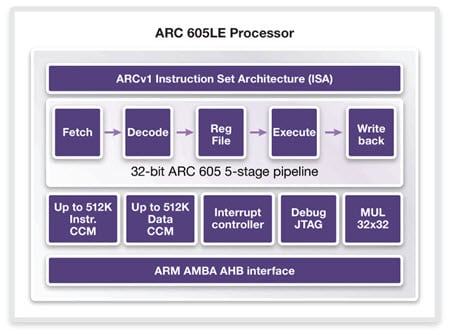

Synopsys’ low-power and compact Synopsys ARC® 605LE pre-configured core is a 32-bit microprocessor that implements the Synopsys ARCompact (ARCv1) 16/32-bit instruction set architecture (ISA). The ARCompact ISA uses 16-bit encodings of frequently used 32-bit instructions, which can be freely intermixed with the 32-bit instructions in the Synopsys ARC 605LE core, increasing throughput, simplifying program flow and providing tighter code density.

With a gate count of around 35K gates in a 130-nm process technology, the ARC 605LE processor offers designers a cost- and power-efficient solution for deeply embedded applications. The ARC 605LE core features Harvard style architecture with single-cycle instruction and data closely coupled memories (CCM), which can be set to be from 512B to 512KB in size. It is targeted for deeply embedded controller applications where small size, low power and 32-bit performance is required.

Highlights & Key Features

- Preconfigured for low power, compact size and performance efficiency

- 1.3 DMIPS/MHz

- Harvard architecture with efficient 5-stage pipeline

- Efficient ARCompact 16/32-bit instruction set

- 512B - 512KB Instruction and Data Closely Coupled Memory (ICCM and DCCM)

- Deterministic and real-time instruction execution

- Area-efficient 32x32-bit multiplier

- Robust tools: MetaWare and MetaWare Lite Development Toolkits

- MQX RTOS support

- As low as 19uW/MHz on TSMC 90-nm LP

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.