The Synopsys IP for PCI Express with Single Root I/O Virtualization (SR-IOV) implements a configurable and scalable SR-IOV solution providing designers with a high-quality IP that reduces risk and improves time-to-market. The silicon-proven Synopsys SR-IOV IP is compliant to the latest PCI Express, PIPE and SR-IOV specifications and has been extensively validated with multiple hardware platforms, PHYs and PCIe verification suites. As the industry standard for PCI Express, Synopsys offers a comprehensive IP solution that is in volume production and has been successfully implemented in a wide range of applications.

The synthesizable core integrates quickly and easily into SoC designs with a user-friendly application interface and conservative timing suitable for a wide range of ASIC and FPGA technologies. The core is available in your choice of datapath widths, PIPE interface widths, and operating frequencies for optimization of size, power, and throughput. Synopsys PCI Express cores are fully compliant with the PCI Express Base Specifications and are used to power the industry's PCI Express compliance testing at PCI-SIG Compliance Workshops.

You can view all Synopsys PCI Express videos here.

You can view all Synopsys PCI Express videos here.

You can view all Synopsys PCI Express videos here.

You can view all Synopsys PCI Express videos here.

Highlights & Key Features

- Designed according to the PCI Express 4.0, 3.1, 2.1, and 1.1 specifications, including the latest errata

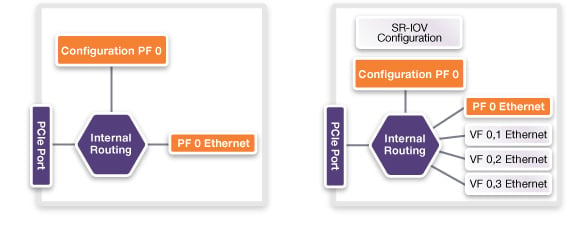

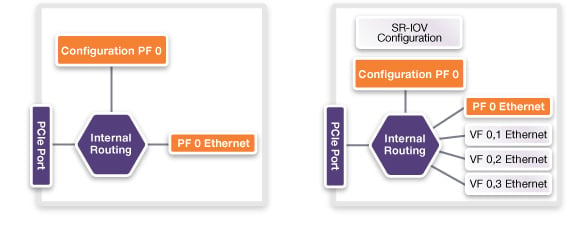

- Designed according to the PCI-SIG Single-Root I/O Virtualization specification

- Supports PIPE PHY interface definition including variable clock and variable data

- Supports 16.0, 8.0, 5.0 and 2.5 Gbps line rates

- Architecture supports x1, x2, x4, x8, and x16 lanes

- Available in 32-, 64-, 128-, 256- and 512-bit data path widths for maximum flexibility

- Support for up to 32 Physical Functions (PFs)

- Support for up to 256 Virtual Functions (VFs), which are dynamically allocated

- Interface for support of the Address Translation Specification

- Alternative Routing ID Interpretation (ARI)

- Function Level Reset (FLR)

- Advanced Error Reporting (AER) supported per VF

- Power Management (PM) per VF supported

- Optimal on-chip memory utilization and low latency

- Legacy PCI, MSI and MSI-X interrupt support

- Multi-function support

- ASIC and FPGA support

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.

Ask Synopsys

i

NOTICE: You are interacting with an AI-powered chatbot that provides general information about Synopsys, including its products and services, which may be incorrect or incomplete. In the event of any conflict or discrepancy, the terms of your applicable agreements supersede any information provided by this chatbot. These chats may be accessed by Synopsys and its service providers to customize the experience and improve this tool, and your use of this chatbot is an agreement to that data processing activity.