The Synopsys ARC-V™ RMX-100 series processors are optimized for use in embedded applications where power and area are the utmost concern.

The ARC-V RMX-100 processors are based on the RISC-V instruction set architecture (ISA) and feature a balanced 3-stage Harvard architecture pipeline that provides sufficient throughput. The ARC-V RMX-100 features up to 64KB of level 1 (L1) instruction cache and up to 2MB each of closely coupled instruction and data memories (CCM).

To enable easy software development, the ARC MetaWare Development Toolkit features a rich software library. The ARC-V RMX-100 processors maintain the high code density and offer excellent performance within a very small footprint.

To maximize PPA of ARC-V RMX Processor-based designs, a Fusion QuickStart Implementation Kit (QIK) that includes tool scripts, a baseline floorplan, design constraints and documentation, is available.

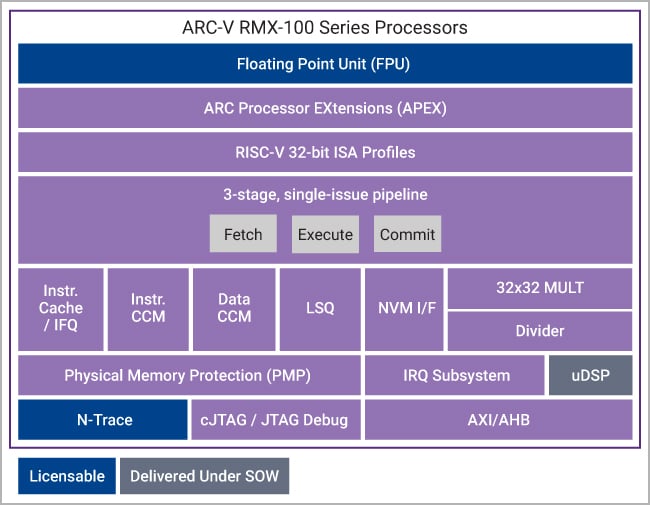

Synopsys ARC-V RMX-100 Block Diagram

![]() Synopsys ARC-V RMX-100 Series Datasheet

Synopsys ARC-V RMX-100 Series Datasheet

Highlights & Key Features

Product Details

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.