New Features for DesignWare DDR3/DDR2 SDRAM Memory Controller IP

The DesignWare DDR3/DDR2 SDRAM memory controllers have been updated to support a number of important new features:

- DesignWare DDR3/2 Memory Controller (MCTL) is now available for use with DesignWare DDR3/2 SDRAM PHYs.

- DesignWare DDR2/3-Lite/mDDR Memory Controller (MCTL) now supports Mobile DDR (mDDR, also known as LPDDR) with DesignWare DDR2/3-Lite/mDDR SDRAM PHYs.

- DesignWare DDR2/3-Lite/mDDR Memory Controller (MCTL) is now available for use with AMBA 2 AHB systems.

DDR3/2 SDRAM MCTL Now Available

Building on successful DDR2/DDR and DDR2/3-Lite SDRAM memory controller designs, Synopsys has released a DDR3/2 SDRAM memory controller compatible with the high performance DesignWare DDR3/2 SDRAM PHYs.

The DDR3/2 MCTL expands on the architecture available in the DDR2/3-Lite MCTL design, adding:

- X4 mode: support for the 4-to-1 data width ratio necessary to support high speed DDR3 up to 1.6Gbps and beyond. This is also known as HDR (half data rate) mode.

- PHY Utility Block (PUB): control for DDR3/2 PHY initialization, data training, and production self-test features.

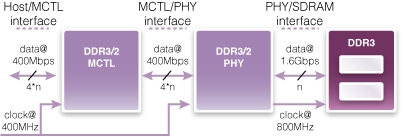

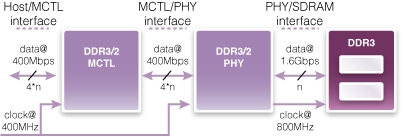

X4 mode allows the MCTL clock to run at a frequency ½ the clock rate of the DDR3/DDR2 SDRAM (and ¼ the data rate). X4 mode allows for easy MCTL synthesis and manageable on-chip clock frequencies without sacrificing bandwidth. The DDR3/2 PHY is responsible for converting the MCTL clock rate and 4x-wide data to/from the MCTL to the DDR clock rate and 1x-wide data to/from SDRAM, allowing the MCTL to operate entirely at a more manageable clock rate. Host ports can be configured to run synchronous or asynchronous to the MCTL clock. Here's an example of X4 mode for a system using DDR3-1600 memory, with synchronous host ports:

The DDR3/2 MCTL also includes the PHY Utility Block (PUB). The PUB is an essential feature for controlling multiple functions of the latest DesignWare DDR3/2 PHYs. After reset, the PUB monitors the PHY for basic initialization completion, then automatically executes data training algorithms to calibrate PHY read/write bit de-skew for data eye widening, read/write DQS centering for widest possible data margins, read DQS gating, and DDR3 write leveling delays. Following initialization and data training, the PUB monitors PHY voltage/temperature (VT) delay drift and automatically compensates for any detected drift, maintaining calibrated PHY delays for reliable data transfers. In addition to PHY VT drift compensation, the PUB monitors I/O VT variation and automatically maintains ODT and impedance calibration for consistent signal integrity. Finally, the PUB provides capabilities for PHY and I/O production test using Built-In Self Test (BIST) algorithms for at-speed loopback testing of the PHY and I/O, eliminating the need for costly high-speed tester time.

DDR2/3-Lite/mDDR SDRAM MCTL New Features

The DDR2/3-Lite SDRAM MCTL has been used in many customer designs, with proven DDR2 and DDR3 SDRAM support up to 1066Mbps. The 2.00a release renames this IP the DDR2/3-Lite/mDDR MCTL and adds major new functionality:

- Mobile DDR support with DesignWare DDR2/3-Lite/mDDR SDRAM PHYs

- AMBA 2 AHB host port support

- Support for DesignWare DDR2/DDR SDRAM PHYs (in DDR2 mode only)

Mobile DDR (mDDR), often referred to as LPDDR, is an attractive SDRAM variation for many power-sensitive applications, such as handheld products. Recent DesignWare DDR2/DDR3-Lite/mDDR PHY releases have added support for mDDR. Now the DDR2/3-Lite/mDDR MCTL has also been enhanced to support mDDR. To support low power applications, the MCTL supports multiple methods to reduce mDDR power consumption. For automatic power savings during idle periods, programmable MCTL time-outs can initiate mDDR Clock Stop and Precharge Power Down. For maximum power savings during extended idle times, the MCTL supports software-initiated mDDR Self Refresh and Deep Power Down. In addition, the MCTL implements address mapping options to more easily take advantage of mDDR Partial Array Self Refresh (PASR), allowing for less-used regions of the mDDR memory array to be run in a much lower power state than active mDDR memory regions. The MCTL supports the full range of mDDR devices from 64Mb x 16 up to 4Gb x 32 and clock frequencies from 0-200MHz, for data rates up to 400Mbps.

In addition to mDDR support, the MCTL has added full support for AMBA 2 AHB on top of existing support for AMBA 3 AXI and the simple, synchronous MCTL host memory interface (HMI). Up to 32 host ports can be individually configured as AHB, AXI, or HMI interfaces. Each port can be configured individually as synchronous or asynchronous to the MCTL clock. MCTL's host ports operate in parallel, allowing transactions from every host port to be accepted simultaneously eliminating system bottlenecks that can reduce SDRAM bandwidth. Bottlenecks are further reduced by supporting AHB split transactions to free up the MCTL host port's AHB bus and maximize AHB bandwidth. AHB split allows multiple outstanding AHB transactions per MCTL host port while the MCTL processes each AHB master's memory request, increasing the effective bandwidth on the SDRAM data bus. MCTL also implements a configurable prefetch algorithm, reducing access latency for long AHB INCR transactions. Configurable-depth AHB data buffers allow for a user-controlled area/performance trade-off.

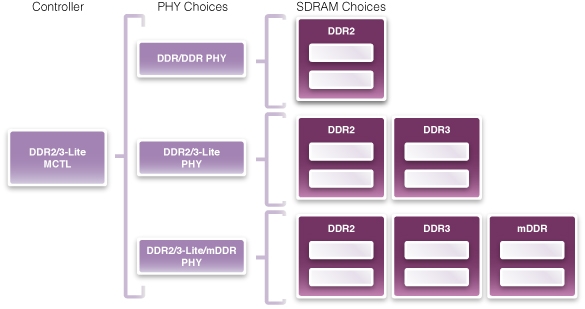

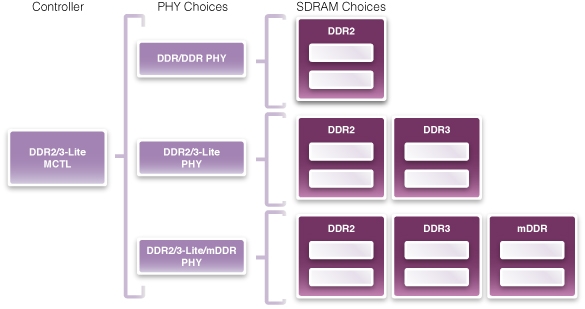

Finally, the DDR2/3-Lite/mDDR MCTL has also added support for the DesignWare DDR2/DDR PHYs, when used with DDR2 SDRAM. This makes DDR2/3-Lite/mDDR MCTL a good match for a wide variety of the DesignWare DDRn PHYs: DDR2/DDR, DDR2/3-Lite and DDR2/3-Lite/mDDR.

More information about all DesignWare DDR3/DDR2/DDR/mDDR SDRAM IP can be found at:

http://www.synopsys.com/DDRn