Cloud native EDA tools & pre-optimized hardware platforms

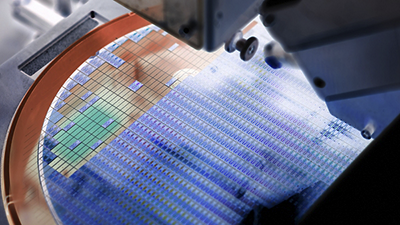

What if you could determine that your semiconductor wafer has problematic dies while it’s being tested, rather than having to wait until the process has completed? Not only would this save a substantial amount of time, but also save the costs associated with testing and packaging up dies that may ultimately fail.

Semiconductor test engineers typically must wait until an entire wafer has been tested—and has moved on in the processing cycle—before they receive test data that tells them about the quality of the dies on the wafer. Testing could span many minutes or even a day, depending on the size of the wafer and the number of tests run on it.

A new machine learning-driven real-time data infrastructure (RTDI) platform is turning test data into actionable insights in milliseconds. Developed by Advantest, the Advantest Cloud Solutions™ (ACS) RTDI™ platform provides low-latency, highly secure data access and system control for semiconductor test operations. It leverages Synopsys Silicon.da real-time production analytics applications to enhance chip quality, yield, and throughput. Mutual customers using this adaptive test applications solution can also achieve improvements in chip power and performance.

Read on to learn how near-instant access to semiconductor test and silicon data gives you better control over silicon quality, while saving test time and enhancing test productivity.

Actionable Semiconductor Yield Insights in Seconds

The traditional semiconductor data collection and analytics process has been a sequential and iterative one, where test engineers must wait for a standard test data format (STDF) file to be produced after a wafer has been tested. By the time the file is delivered, the wafer will have moved on to the assembly and packaging steps. At this point, test engineers may learn that a few of the dies on the wafer are risky. For instance, these dies may be deemed marginally good dies, but they’re at the rim of the test limits for quality. As such, the engineers may want to discard them, rather than risk packaging them for shipment. This involves finding and intercepting the wafer in question and bringing it back into the testing system. The situation can also be handled at assembly by changing the wafer map and downgrading the dies of interest.

With the adaptive test applications solution, semiconductor test data that is securely collected, analyzed, stored, and monitored by ACS RDTI flows in real-time straight into Silicon.da.There, the information is processed with other data collected (such as from in-chip monitors) and analyzed for actionable insights. Since test engineers can now identify potential die issues while the wafer is being tested, they can take corrective action early on, without wasting time on the tester. The same process applies at the assembly phase, where dies are cut and placed into their own packages. As packaged dies go through a similar series of testing, real-time data funneled into Silicon.da analytics running on ACS RTDI provides engineers the insight they need to pull and discard problematic packages before they are shipped for integration into their end products.

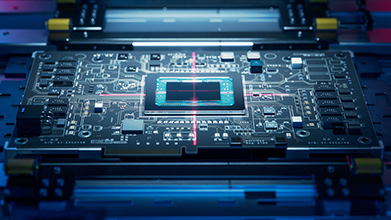

Silicon.da, which can be run on-prem or in the cloud, is part of the Synopsys Silicon Lifecycle Management (SLM) family, which provides in-chip silicon health monitoring and analytics throughout the device lifecycle. Analytics derived from Silicon.da can also run in real-time while the device is being tested using ACS RTDI. Today’s semiconductor landscape is being shaped by scale and system complexity, increasingly aggressive quality requirements, and a packaging evolution that is giving rise to complex new architectures such as multi-die systems. In the face of these trends, on-board silicon monitoring from SLM technologies is becoming increasingly critical for ensuring lasting chip reliability and performance levels. Since the semiconductor development process can generate petabytes of data, technology such as Silicon.da can help make sense of it all, providing automated root-cause analysis, highlighting silicon data outliers, and consolidating analytics across all semiconductor manufacturing phases into a single, shareable environment.

Use Cases for Adaptive Semiconductor Test Applications

Determining the root cause of silicon issues calls for deep insight into the part’s operation. This comes from data collected by in-chip monitors, along with test measurement data. For example, say there’s a timing failure detected during system-level test. In this case, path margin monitors can identify the failing path, thermal sensors can tell us about a change in the thermal gradient, and voltage monitors can indicate any significant voltage drop.

The in-chip monitors are read during the testing process, with the data streamed along with test measurement data from ACS RDTI into Silicon.da applications running on ACS RTDI. Machine learning models from Silicon.da help generate actionable insights. Another use case to consider is VMIN, the minimum voltage at which a device can run. Typically, determining VMIN on the tester is an exhaustive undertaking, requiring lots of test time to consider a myriad of corner cases. Silicon.da uses user-trained machine learning models to predict VMIN performance, reducing test time.

Adaptive test limit setting is another valuable use case of the ACS RDTI and Silicon.da solution. During test program execution, test limits are traditionally set based on methods such as dynamic part average testing (DPAT), which produces fixed sensitivity limits that apply to all the parts in a wafer. But what if there was a way for each part to have its own limits for higher accuracy on parameters such as speed and power consumption during testing? Ultimately, this could help lower defective parts per million (DPPM) and result in higher quality wafers. By correlating in-chip sensor data for process, voltage, and temperature with test measurement data, and adjusting the limits for each die on-the-fly, test engineers can better determine which die are outliers and which are actually good.

Strengthening the Next Generation of Semiconductor Test

Data analytics and the power of machine learning will shape the next generation of semiconductor test, providing test engineers with deeper insights for better quality of results and time to results. Advantest’s ACS RDTI platform along with Synopsys’ Silicon.da are forging a more cohesive test ecosystem. With their adaptive approach replacing a traditionally iterative one, test engineers can benefit from operational efficiencies, reduced test costs, and, ultimately, higher yields. To learn more about Silicon.da visit our website. And to see more about ACS Real-Time Data Infrastructure, please refer to this web page.