The Synopsys ARC® 710D configurable processor core is designed for embedded processing functions within system-on-chips (SoCs). The ARC 710D processor core is optimized for hard, real-time processing, where high speed and deterministic response are required. Small size, low power and configurable architectural features make the ARC 710D processor core ideal for multi-core and other applications.

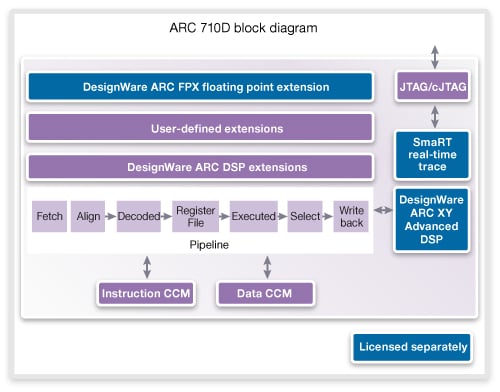

Powerful DSP options enable the Synopsys ARC 710D processor core to perform more of the functions on the SoC, eliminating the need for separate logic or DSP blocks. Optionally, custom instruction extensions may be incorporated to achieve application performance levels unattainable with fixed architecture cores.

The Synopsys ARC 710D processor core is supported by a full suite of software and hardware development tools. The suite includes the MetaWare Development Kit, which generates highly efficient code that is ideal for embedded applications and ARC simulators including xCAM and nSIM, and the ARChitect configuration tool.

Highlights & Key Features

- A highly configurable architecture allows SoC designers to include only the core features that are required for their specific application, resulting in smaller die size and lower power than can be achieved with a fixed core.

- User-defined instruction and register extensions deliver 5 - 100 times performance improvement of critical routines.

- Cacheless design and closely coupled (single-cycle) memories provide fast, predictable computation.

- Built-in DSP features include instruction and register extensions that accelerate signal processing algorithms.

- Optional Synopsys ARC XY Advanced DSP subsystem delivers the performance of dedicated DSP cores.

- Synopsys ARCompact™ 16- / 32-bit Instruction Set Architecture reduces code size by up to 40 percent compared to 32-bit only instruction sets.

- Inter-processor communication ISA support, multi-processor debug environment and flexible interfaces enable multi-core designs.

- JTAG debug port and optional embedded hardware breakpoints facilitate software debug.

- Delivered as synthesizable RTL source code (Verilog®), the Synopsys ARC 710D core is fully compatible with industry standard design methodologies and tool flows.

Product Details

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.