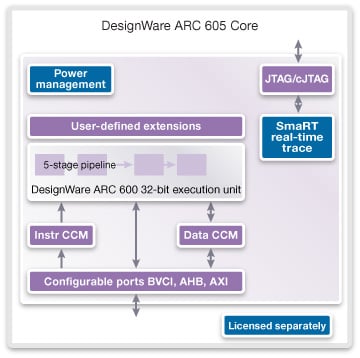

Designed for a broad range of embedded control functions within SoCs, the ARC 605 has a full 4GB addressing range and support for a Power Management Unit (PMU) that offers advanced power management capabilities. Based on a Harvard architecture the 605 features single-cycle close coupled memory (CCM) for both instruction and data spaces. The cacheless design provides fast and deterministic processor performance for embedded applications. User defined custom instruction extensions may be incorporated by the user to achieve even higher performance levels. The processor is implemented with the efficient ARCompact 16-/32-bit Instruction Set Architecture (ISA) that reduces code size by up to 40% compared to 32-bit-only instruction sets.

The Synopsys ARC 605 is highly configurable and can be quickly and easily customized for a specific application, so designer can include only the features that they need minimizing power consumption and cost, while maximizing performance. The 605 is supported by a full suite of software and hardware development tools. The suite includes the MetaWare Development Kit that generates highly efficient code ideal for embedded applications, the ARC simulators including xCAM and nSIM, and the ARChitect configuration tool.

Highlights & Key Features

- Developed for embedded SoC applications

- Harvard architecture with 5-stage, 32-bit pipeline

- 32-bit address and data busses (4GB address space)

- 16 or 32 entry 32-bit general purpose register file, extendible to 60 registers

- 1 KB - 512 KB Instruction Close Coupled Memory (ICCM)

- 2 KB - 256 KB Data Close Coupled Memory (DCCM)

- Deterministic and real-time instruction execution

- Efficient ARCompact 16/32-bit instruction set

- AHB, AXI or BVCI peripheral bus interface

- 32-bit auxiliary register space with single-cycle data storage and retrieval

- Up to 32 user configurable interrupts

- Optional 16x16 and 32x32 multipliers

- Optional 32-bit barrel shifter

- Zero overhead loop counter

- Optional CRC, normalize, swap instructions

- Support for custom instruction extensions

- Supported by a full suite of development tools

- JTAG debug interface with multi-core debug support

- Delivered as synthesizable RTL source code (Verilog)

Product Details

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.