## A Quick Guide to Synopsys University Program Resources

Courseware, SolvNetPlus & Synopsys Learning Center

University Program, Synopsys Taiwan June 2022

## CONFIDENTIAL INFORMATION

The information contained in this presentation is the confidential and proprietary information of Synopsys. You are not permitted to disseminate or use any of the information provided to you in this presentation outside of Synopsys without prior written authorization.

## IMPORTANT NOTICE

In the event information in this presentation reflects Synopsys' future plans, such plans are as of the date of this presentation and are subject to change. Synopsys is not obligated to update this presentation or develop the products with the features and functionality discussed in this presentation. Additionally, Synopsys' services and products may only be offered and purchased pursuant to an authorized quote and purchase order or a mutually agreed upon written contract with Synopsys.

## Contents

- Membership Benefit

- Teaching Resources

- courseware, generic libraries, PDKs

- Knowledge Base

- SolvNetPlus

- Synopsys Learning Center

## Contents

- Membership Benefit

- Teaching Resources

- courseware, generic libraries, PDKs

- Knowledge Base

- SolvNetPlus

- Synopsys Learning Center

## Membership Benefits

#### IC Design and EDA Curriculum:

- Full Semester Courses 80+ courses for Bachelor and Master programs

- Workshops/Lectures 30 courses

- Short Lectures/Labs 28 courses

#### **Teaching Support:**

- 32/28nm & 90nm Generic Libraries and iPDK's

- Generic Memory Compiler

#### Access Synopsys knowledge base:

- Document contains product release note, installation guide, user guide

& reference manual

- Search provides an advanced search engine to retrieve information from various sources, such as documentation, articles, training, and so on.

- **Training** Access **Synopsys Learning Center** for free self-paced training resources. The approved academic users are entitled to the **"Elite"** subscription model. Find more details <u>here</u>.

<sup>\*</sup>Requires SolvNetPlus account to access above-mentioned resources.

## Contents

- Membership Benefit

- Teaching Resources

- courseware, generic libraries, PDKs

- Knowledge Base

- SolvNetPlus

- Synopsys Learning Center

## Teaching Resources

#### IC Design and EDA Curriculum:

- Full Semester Courses 80+ courses for Bachelor and Master programs

- Workshops/Lectures 30 courses

- Short Lectures/Labs 28 courses

#### **Teaching Support:**

- 32/28nm & 90nm Generic Libraries and iPDK's

- **Generic Memory Compiler**

#### Access through:

#### www.synopsys.com/community/university-program.html

#### SYNOPSYS°

SILICON DESIGN & VERIFICATION SILICON IP SOFTWARE INTEGRITY ABOUT US

/ Community ▼ / University Program ▼

#### Electronic Design University Program

Education for Smart, Secure Everything

"Access to Synopsys' leading-edge design software enables our engineering students to learn in the same environment as their industry counterparts, increasing the value of the student experience and research at Purdue University." - Dr. Mark C. Johnson, Purdue University

free online resource for

developers of embedded

Visit the DesignWare ARC product store to order your development kits and start designing today!

The embARC Community is a

applications for ARC processors.

#### MEMBERS ONLY LOG IN

Access curricula and resource downloads (SolvNetPlus ID and password required)

#### Curriculum Programs

curriculum, and more.

Courseware for Teaching IC Design with Synopsys Tools.

Learn More

#### Teaching Resources

Through our Electronic Design University Program we aim to inspire and foster the world's next generation

tools and technology needed to prepare highly-skilled graduates ready to work in the world of Smart, Secure

Everything. Membership in the program includes access to leading-edge EDA software, technical support,

of technologists and innovators by providing academic and research institutions with access to the EDA

Synopsys Generic Libraries, PDKs, and Memory Compiler

Learn More

#### Support & Training

Technical Support and Tool Training for Universities

Learn More

#### Contact Us

Ask questions, request information, and inquire about membership in the Electronic Design Academic Program

## **Teaching Resources**

IC Design and EDA Curriculum

## or

## IC Design Courses

# Bachelor

- Analog and Mixed-Signal IC Physical Design

- Analog Integrated Circuits

- Computer Architecture and Engineering

- Digital Integrated Circuits

- IC Design Flow

- IC Design Introduction

- IC Testing

- IC Synthesis and Optimization

- Introduction to Microelectronic Circuits

- IC Synthesis and Optimization

- Introduction to Semiconductor Devices

- Linear Algebra

- Logic Design

- Microprocessor Systems

- Numerical Methods

- Scripting Languages for Beginners

- Static Timing Analysis

- Synthesis and Optimization of Digital Integrated Circuits

- Technical Writing

## Master

- Analog Modeling with Verilog-A

- ARC Processor-Based Embedded Programming

- Complex Functions

- Crosstalk and Noise

- Design for Test

- Design of Embedded Systems

- Design of Special I/O's

- Digital Signal Processing

- EDA Tools

- FPGA Prototyping

- IC Design for Thermal Issues

- IO Design

- Low Power Design

- Low Power Design with Synopsys 32/28nm Generic Library

- Mixed-Signal IC Design

- Modeling and Optimization of IC Interconnects

- Rad-hard IC Design

- RF IC Design

- Synopsys EDA Tool Flow for Front-End Digital IC Design

- Synopsys EDA Tool Flow for Back-End Digital IC Design

- Thermal and Electro-Thermal Simulation: Achievements and Trends

# Short Lectures

# Workshops

## Short Lectures and Workshops

#### - Basic Perl Programming

- Characterization with SiliconSmart

- Circuit Simulation Transient Analysis

- Compiler Optimization and Code Generation

- Computer Networks

- Digital Design with Verilog

- Digital System Design and Simulation with VHDL

- Embedded Systems Design

- How to Create an Interoperable PDK

- IC Fabrication

- IC Simulation Theory

- Introduction to RF Communication

- Introduction to Verilog HDL

- Low Power Design w/Synopsys 32/28nm Generic Library

- Low Power Methodology Manual for 32/28nm

- Operational Research

- Optimization Methods

- Physical Verification Russet Development

- Power-Performance Optimization of Digital Circuits

- Process Variation Aware Design

- RF Circuits

- Scripting Languages

- Sequential Elements

- Signal and Power Integrity

- Statistical Techniques for Timing Analysis

- Subthreshold Design and Implementation

- Synthesizing OpenSPARC with 32/28nm EDK

- Techniques for Circuit Simulation

- User Interface Design

- Verification Methodology for Low Power

#### Advanced Design of Digital Circuits for Specific Applications

- ASIC Design Flow Tutorial Based on Synopsys 32/28nm Library

- ASIC Design Flow Tutorial Based on Synopsys 90nm Library

- Chip Design

- Computer Arithmetic Applied to High-Performance Cryptography

- Design for Testability

- Full Custom IC Design Flow with Synopsys Custom Tools

- Project Management

- Software Methodology Module for Custom Designer

- Synopsys Design Flow Tutorial

- Synopsys IC Design Flow Based on 90nm Generic Library

- SystemVerilog Verification Tutorial

- TCAD Course

- TCAD for VLSI Design

- TCAD Quick Start Guide

- TCAD Short Course

- Universal Verification Methodology

## Full Semester Courses

- Topics cover all aspects of IC/SoC design

- Courseware for Bachelor and Master level programs

- Full-semester courses contain ~15 weeks of material and include the following components

## **Teaching Resources**

Teaching Support (Generic Libraries, PDKs, Generic Memory Compiler)

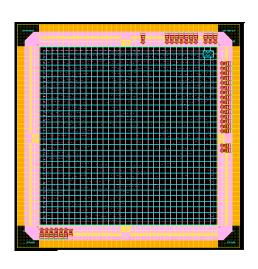

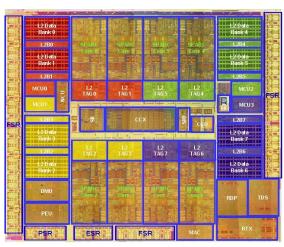

## Generic Libraries (EDK)

- 32/28nm and 90nm

- Enables students to master advanced design methods using the latest Synopsys EDA tools

- Includes:

Digital Standard Cell Library I/O Special Cell Library Embedded Memories

Phase Locked Loop Low Power Memories Reference Designs

Used by Synopsys for:

#### Curricula Development

To support development of laboratory works and course projects.

#### **Customer Education**

To train customers with Leon3 and ORCA processors' design.

#### Global Technical Services

To train internal staff and customers on Synopsys tools and low power flows.

#### **Application Consultants**

To develop and test sample designs and Reference Methodology scripts.

## Interoperable Process Design Kits (iPDKs)

- 32/28nm and 90nm

- Enables students to master AMS/Custom design with the Synopsys custom implementation tool suite

- Includes:

Technology Files

Physical Verification Files

Parasitic Extraction Files

**HSPICE Models**

Symbol Library and Python PCells

Callback Scripts

**Embedded Memories**

Setup Files

#### Curricula Development

To support development of laboratory works and course projects.

#### **Customer Education**

To train customers with Leon3 and ORCA processors' design.

#### Global Technical Services

To train internal staff and customers on Synopsys tools and low power flows.

#### **Application Consultants**

To develop and test sample designs and Reference Methodology scripts.

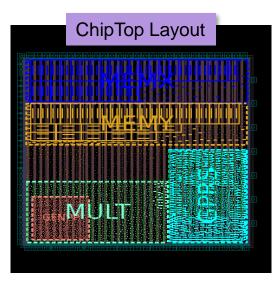

## Reference Designs Supported by Synopsys EDKs

- DesignWare® ARC 600 Academic Core 32-bit RISC processor core optimized for embedded applications and DSP tasks

- ARM® Cortex® M0 DesignStart™ Processor Entry-level configuration of ARM Cortex-M0 microprocessor¹

- OpenSPARC T1 64-bit multicore processor<sup>2</sup>

- **LEON3** 32-bit embedded processor<sup>2</sup>

- Sample Processor Designs included in EDK

- ORCA for timing analysis

- ChipTop for low power design

- 1. Available through ARM DesignStart for Processor IP portal

- 2. Available via GNU General Public License

## DesignWare ARC 600 Processor Design

- Synthesis scripts optimized for 32/28nm EDK that can be used to easily redesign the academic version of the ARC 600 processor

- Synopsys curriculum for the ARC 600

- IC Synthesis Based on DesignWare ARC 600 Core, includes:

- Lecture slides

- Covers ARC 600 details and EDA tool use

- Laboratory works

- Step-by-step guide of the ARC 600 design process

Apply in Members Only for access to the DesignWare ARC 600 Academic Core: <a href="https://www.synopsys.com/apps/protected/university/members.html">https://www.synopsys.com/apps/protected/university/members.html</a>

## ARM Cortex-M0 DesignStart Processor Design

- Complete Synthesizable Solution

- Pre-configured Verilog netlist derived from commercial Cortex-M0 processor

- Simple testbench

- Example test code

- Scripts to implement the ARM Cortex-M0 DesignStart design using Synopsys 32/28nm EDK and EDA tools

- Synopsys curriculum for the ARM Cortex-M0

- IC Synthesis Based on ARM Cortex-M0 DesignStart Processor

Download from ARM DesignStart for Processor IP portal: http://arm.com/products/processors/designstart-processor-ip

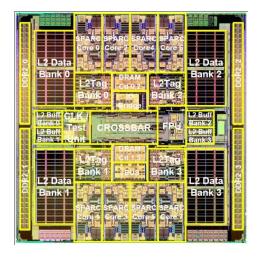

## OpenSPARC Processor Design

- Scripts to enable OpenSPARC design using Synopsys 32/28nm EDK and Design Compiler

- Implemented low power design techniques

- Synopsys curriculum for OpenSPARC

- Computer Architecture

- Includes:

- Physical design scripts for IC Compiler

- Scripts to enable small block reuse for educational purposes

- Various lab projects based on small blocks

Download OpenSPARC: <a href="http://www.opensparc.net">http://www.opensparc.net</a>

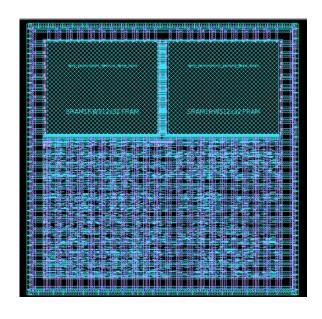

## Synopsys Generic Memory Compiler

- Configurable software that automatically generates static RAM circuits of different types and sizes with all required deliverables

- Generate custom memory instances for educational ICs

- Designed for use with Synopsys EDKs and EDA tools

- Optimized for the Synopsys Digital Design Flow

- Supports multiple technologies (90nm, 32/28nm, etc.)

#### **User interface**

- Command line

- GUI

#### **Supported memory types**

- 1 port SRAM

- 2 port SRAM

- 1 port Low Power SRAM

- 2 port Low Power SRAM

"Using the Synopsys Generic Memory Compiler in our complex processor for DSP application was a **great time-saving tool**. It helped the students generate the SRAM they wanted in a snap, saving them critical time to concentrate on the rest of the complex design."

Dr. Maged Ghoneima, American University in Cairo

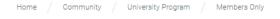

## Get started w/ Teaching Resources

Link: www.synopsys.com/community/university-program.html

## 01 Go to Electronic University Program website

Select the Teaching Resources that you need, then click on "Members Only website".

#### Curriculum Link: www.synopsys.com/community/university-program.html

Synopsys provides universities with access to comprehensive curricula for Bachelor and Master Programs in IC design and EDA development.

Each full-semester course contains 15 weeks of material including syllabus, lectures, labs, homework and exams. Synopsys tools are applied in the labs for a thorough and practical understanding of theoretical concepts introduced in each course. Professors at member universities may use these course materials to implement a new course or to supplement content in an existing course.

All coursewere described below may be downloaded from the Synopsys Electronic Design University

Program Members Only website (received Sch Net ID and password). If your university is not yet a ment

of the Synopsys Electronic Design on iversity Program and you would like to apply, please contact us.

**Master Degree Courses:**

· Complex Functions

· Crosstalk and Noise

• Design of Special I/O's

· Digital VLSI Design

FPGA Prototyping

EDA Tools

• Digital Signal Processing

Design for Test

· Analog Modeling with Verilog-A

• Design of Embedded Systems

ARC Processor-Based Embedded Programming

#### Full Semester Courseware

#### **VLSI Design Curriculum**

#### **Bachelor Degree Courses:**

- · Analog and Mixed-Signal IC Physical Design

- · Analog Integrated Circuits

- · Computer Architecture and Engineering

- Digital ASIC Design (NCSU)

- Digital Integrated Circuits

- IC Design Flow (RAU)

- IC Design Introduction

- 10 Deolgii miliodadello

- IC Simulation Theory

- IC Testing

- Introduction to Logic Design (SU)

- Introduction to Microelectronic Circuits

#### TI 1.000

The embARC Community is a free online resource for developers of embedded applications for ARC processors.

#### ARC DEVELOPMENT KITS

#### Visit the DesignWare ADC

product store to order your development kits and start designing today!

#### MEMBERS ONLY LOG IN

Access curricula and resource downloads ( SolvNetPlus ID and password required)

#### Contact Us

Ask questions, request information, and inquire about membership in the Electronic Design Academic Program

- Requires a SolvNetPlus account to sign in.

- Please contact Synopsys

University Program Taiwan

(chunhsu@synopsys.com) for

membership enquiry.

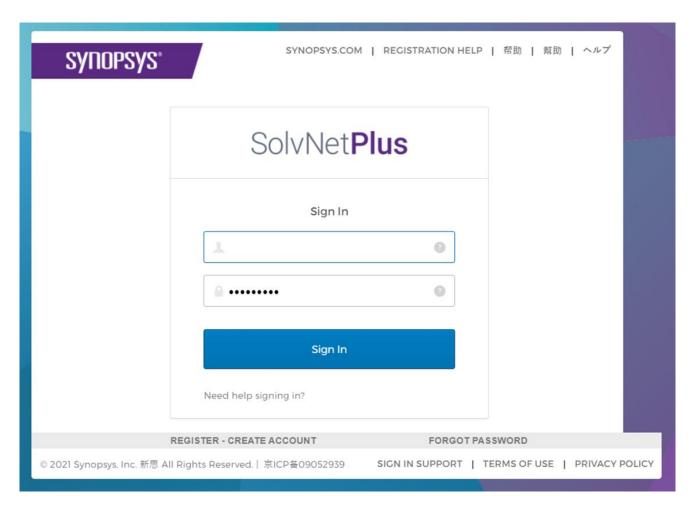

## 02 Log-in with Synopsys SolvNetPlus credential

https://www.synopsys.com/apps/protected/university/members.html

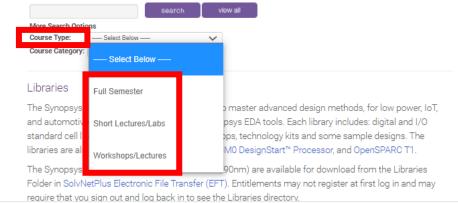

## 03 Insert course name in the search engine

### Search by "Course Type"

#### Members Only

Note: Use of the material downloaded from Members Only is subject to the terms and conditions of the End User License Agreement executed between your company and Synopsys. You can use the material at your site but you cannot distribute or publish it externally. Third party material located on this site is included with the permission of the owner (who retains all rights), and is provided solely for your convenience. Synopsys does not endorse and is not responsible for such third party content, and any use of these materials should be conducted only with the permission of the owner.

Go to: Curriculum | Libraries | PDKs | Memory Compiler | Processor IP

#### Curriculum

Synopsys provides universities with access to a comprehensive curriculum for Bachelor and Master Programs in microelectronic design and EDA development. Course materials can be used to implement a new course or to supplement content in an existing course. Search courses by keyword or course type to find and download courses quickly and easily.

Please report any errors or inconsistencies in these materials to our University Program team.

#### **Keyword Search:**

#### ARC EM STARTER KIT

The new ARC EM Starter Kit is now supported by the embARC Open Software Platform.

#### MEMBERS ONLY LOG IN

Access curricula and resource downloads ( SolvNet ID and password required)

#### Contact Us

Ask questions, request information, and inquire about membership in the University Program

#### **Course Type:**

- 1. Full Semester

- 2. Short Lectures / Labs

- 3. Workshops / Lecturers

## 03 Insert course name in the search engine (cont.)

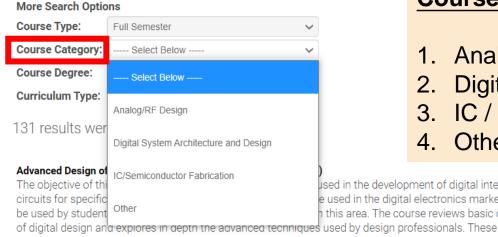

## Search by "Course Category"

Example: Full Semester

#### **Course Category:**

- 1. Analog / RF Design

- Digital System Architecture and Design

- 3. IC / Semiconductor Fabrication

- 4. Other

used in the development of digital integrated e used in the digital electronics market and will this area. The course reviews basic concepts

techniques involve ways of dealing with complex systems, ways to create faster systems, methodologies for design verification and evaluation of results. The course covers and compares the use of VHDL and Verilog, and the impact of coding style on final results. Note: This course can be used with permission from the 3rd party owner. All rights reserved.

> Lectures (18 MB)

#### Advanced Methods in Logic Synthesis and Equivalence Checking

The goal of the course is to study logic synthesis problem, logic optimization as well as advanced methods in synthesis. The course also focuses on logic design components and combinational and sequential equivalent checking.

- > Syllabus (88.0 KB)

- > Lectures (3,135,241 bytes)

- > Labs (657 KB)

- > Homework (263 KB)

- > Labs & Homework (441 KB)

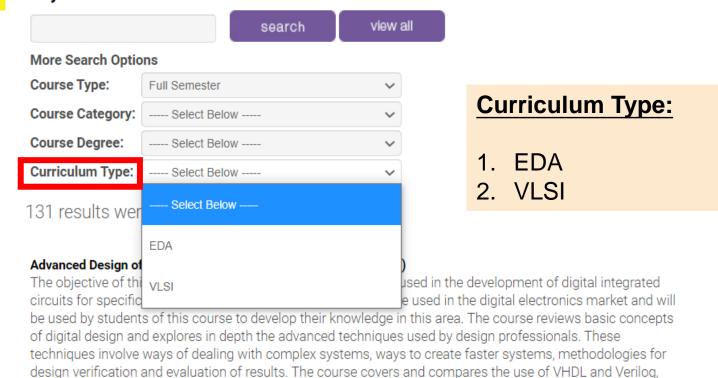

## 03 Insert course name in the search engine (cont.)

## Search by "Curriculum Type"

Example: Full Semester

#### **Keyword Search:**

and the impact of coding style on final results. Note: This course can be used with permission from the 3rd

> Lectures (18 MB)

party owner. All rights reserved.

## 04 Access to the courseware

#### Start to download course syllabus, lecturer slides, labs or exams

Example: Full Semester

#### **Keyword Search:**

49 results were found under 'Full Semester' Course Type, 'VLSI' Curriculum Type.

#### Analog and Mixed-Signal IC Physical Design

This course covers the basics of IC design, custom design flows. The course mainly focuses on data of analog and mixed-signal IC physical design

- > Syllabus (90 KB) > Lectures (4.6 MB)

- > Labs (1.6 MB)

- > Homework & Exams (244 KB)

#### **Analog Integrated Circuits**

The goal of the course is to study principles of design, analysis and simulation of analog integrated circuits. The course also focuses on variants, parameter improvement methods, parameters analysis of different basic analog circuits: differential and operational amplifiers, switched capacitor circuits, oscillators, phase looked

ver sources, etc.

> Syllabus (42 KB) > Lectures (17 MB) > Labs (12 MB) > Project (663 KB) Homework & Exams (480 KB)

#### **Course Contents:**

- 1. Syllabus

- Lectures

- Labs

- Project

- 5. Homework & Exams

## Contents

- Membership Benefit

- Teaching Resources

- courseware, generic libraries, PDKs

- Knowledge Base

- SolvNetPlus

- Synopsys Learning Center

## **Knowledge Base**

#### Access Synopsys knowledge base:

- Document contains product release note, installation guide, user guide & reference manual

- Search provides an advanced search engine to retrieve information from various sources, such as documentation, articles, training, and so on.

- Training Access Synopsys Learning Center for free self-paced training resources. The approved academic users are entitled to the "Elite" subscription model. Find more details here.

####

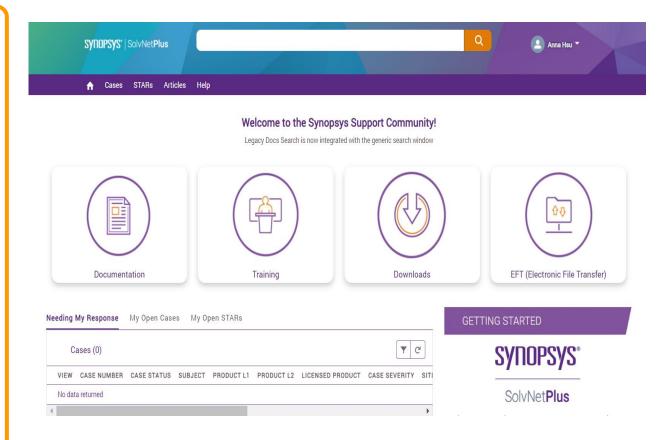

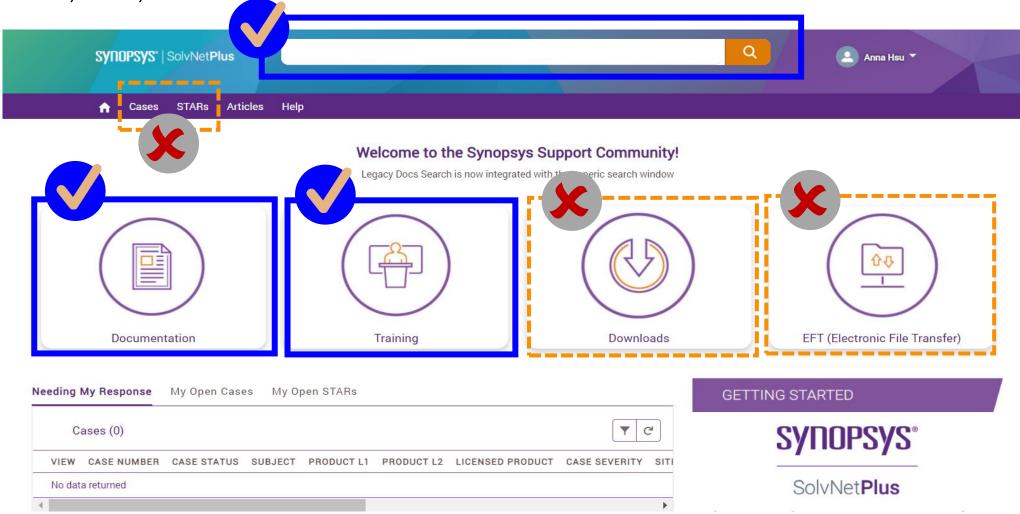

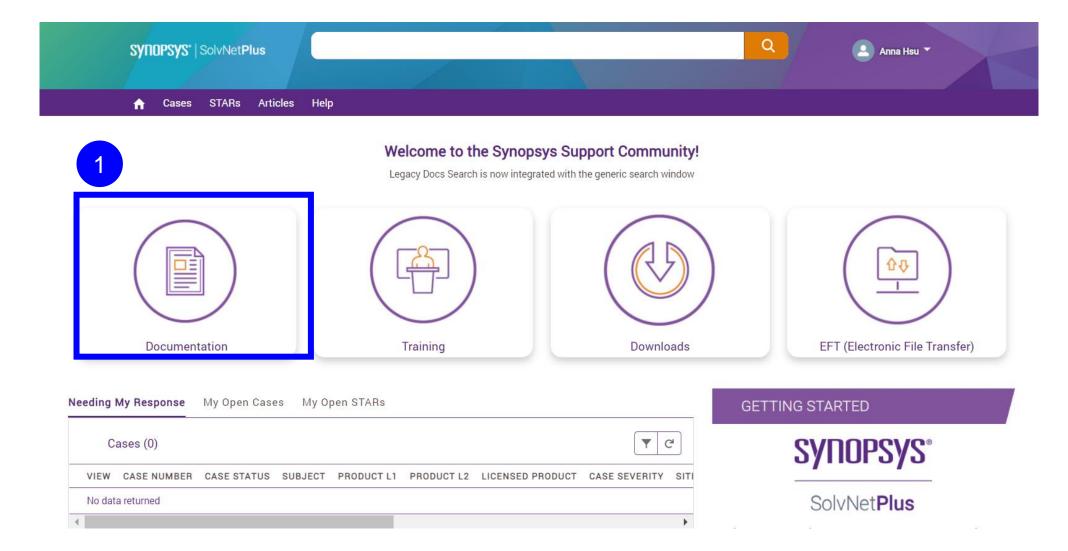

## Get Oriented with SolvNetPlus

University users can access Documentation, Training & Search; but CANNOT access Download, EFT, Cases & STARs.

## **Knowledge Base**

SolvNetPlus (Documentation & Search)

## Get started w/ SolvNetPlus

https://solvnetplus.synopsys.com/

## 01 Log-in with Synopsys SolvNetPlus credential

https://solvnet.synopsys.com/

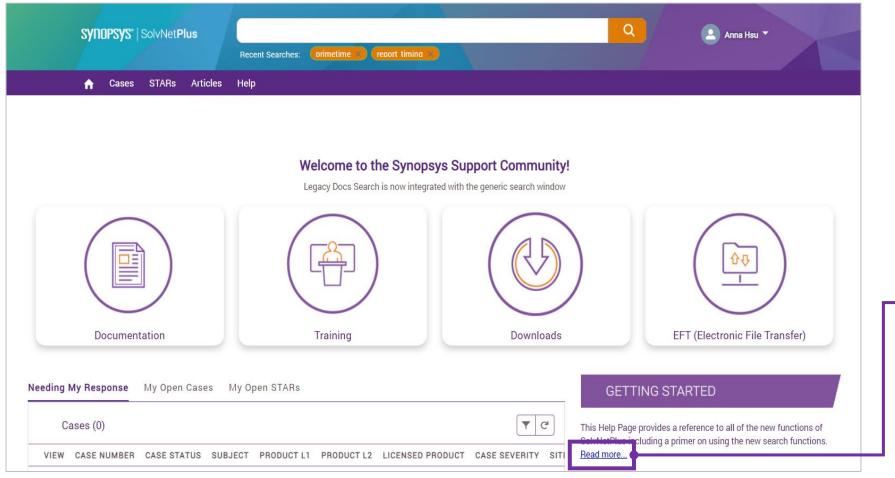

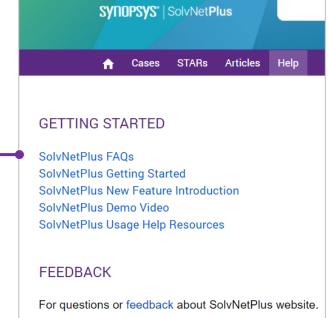

## 02 Read "GETTING STARTED" before use

## 03 Click on "Documentation"

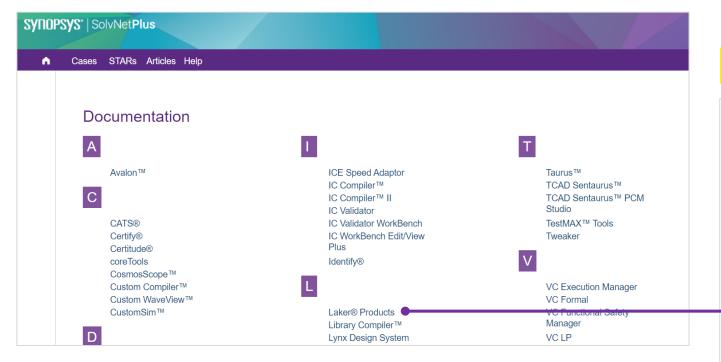

## 04 Search by product name to get tool documents

You can download release notes, installation guides & user guides and reference manuals from this section

Example: Laker

#### Laker

#### Laker3, L-2018.06, June 2018

- 🔼 Laker3 Installation Guide

- Laker3 Quick Start Guide for Laker3 User Interface, K-2015.06, June 2015

- Laker3 Command Reference Manual, K-2015.06, June 2015

- Laker3 Tcl Reference Manual, K-2015.06, June 2015

- Laker3 Bind Key Summary

- 🔼 Laker3 Menu Summary

- Laker DRD Tcl Command Reference, K-2015.06, June 2015

- Laker CDPR LEF/DEF Tutorial, 2013.02, February 2013

- Laker CDPR Data Preparation and SDL Tutorial, 2013.02, February 2013

- Laker3 Release Notes Version, L-2018.06-SP1 (January 2019)

#### Laker, 2020.03, March 2020

- Laker User Guide and Tutorial, 2015.03

- Laker Command Reference, 2015.12

- 🔼 Laker Tcl Reference, 2015.12

- Laker Bind Key Summary, 2015.12

- Laker Command Index, 2015.12

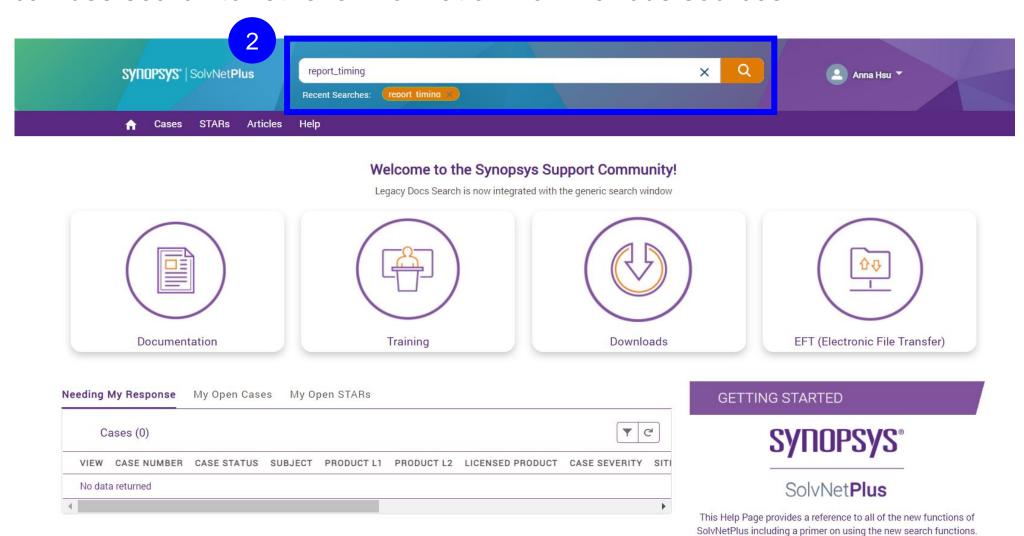

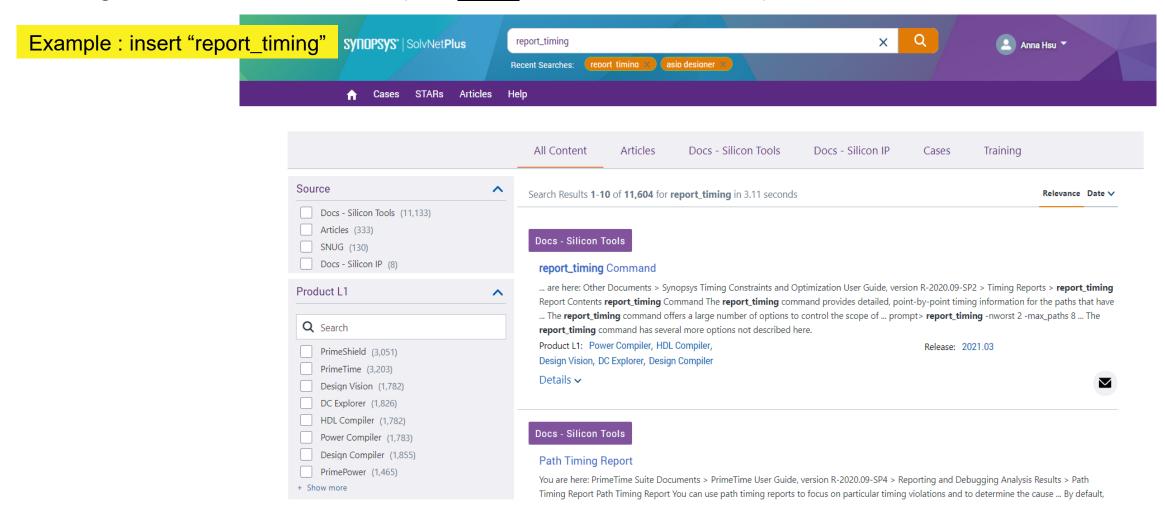

## 05 Look for information in the "Search" bar

You can use search to retrieve information from various sources

### 06 Choose needed info from the displayed search results

The information will be displayed from various sources, such as documentation, articles, training, YouTube, and so on (but *NOT* in cases & STARs)

# **Knowledge Base**

Synopsys Learning Center (Self-paced Learning)

- 1. Access via SolvNetPlus (<a href="https://solvnet.synopsys.com/">https://solvnet.synopsys.com/</a>)

- 2. Access via Synopsys Learning Center (<a href="https://www.synopsys.com/support/training/self-paced.html">https://www.synopsys.com/support/training/self-paced.html</a>)

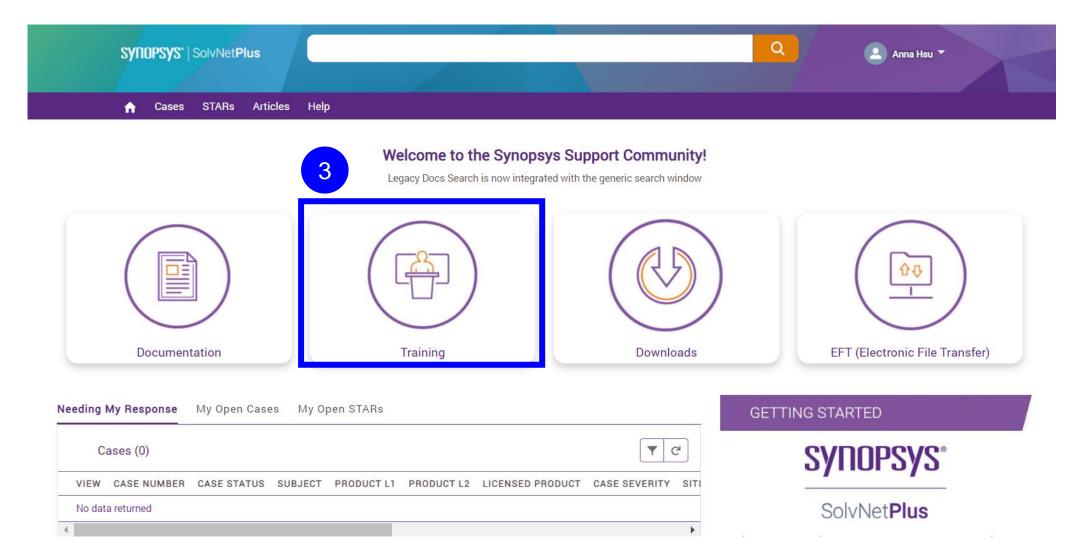

### 01 Login SolvNetPlus and click "Training"

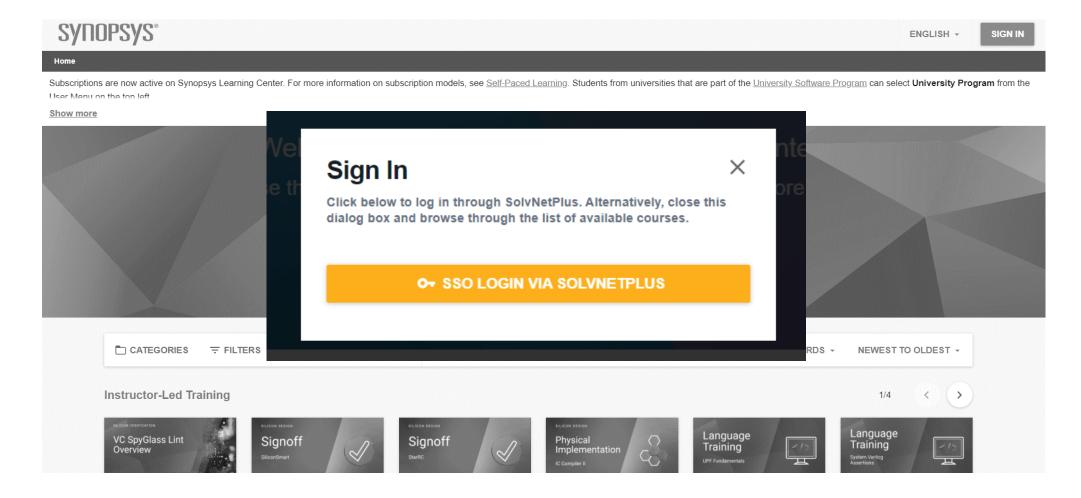

### 02 SSO Login via SolvNetPlus

# 02 Access Synopsys Learning Center

√ You can also directly access through: <a href="https://training.synopsys.com/">https://training.synopsys.com/</a>

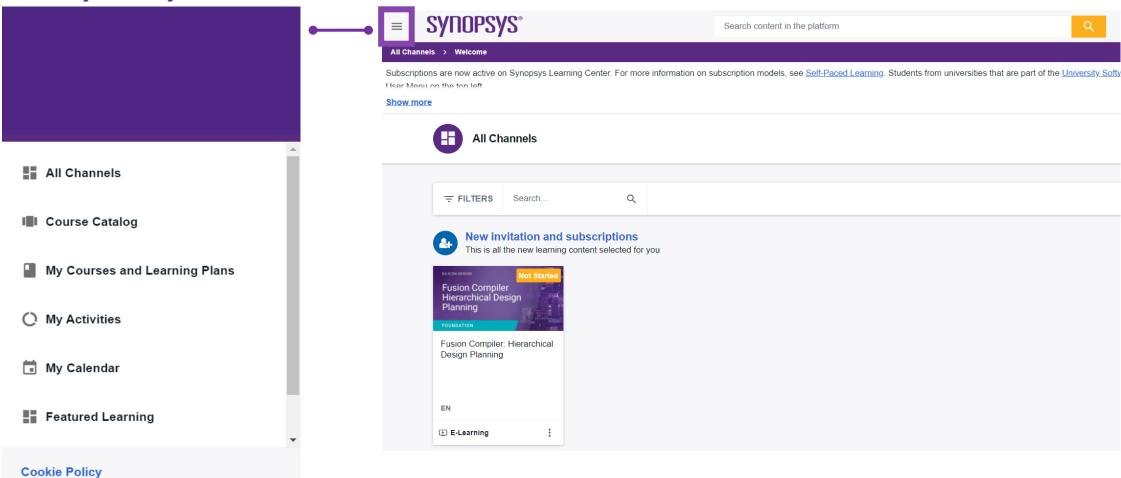

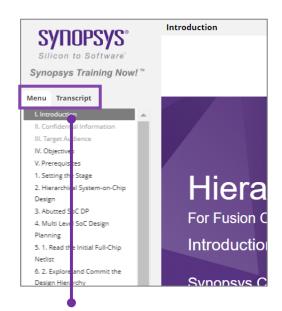

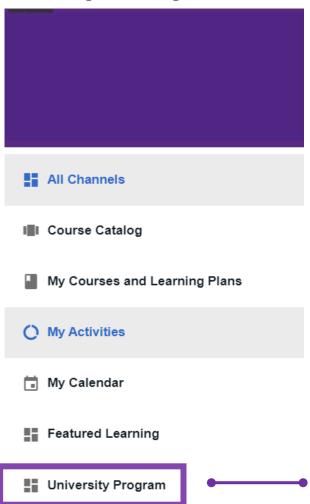

### 03 Click on "三"

$\times \quad \text{Synopsys}^{\circ}$

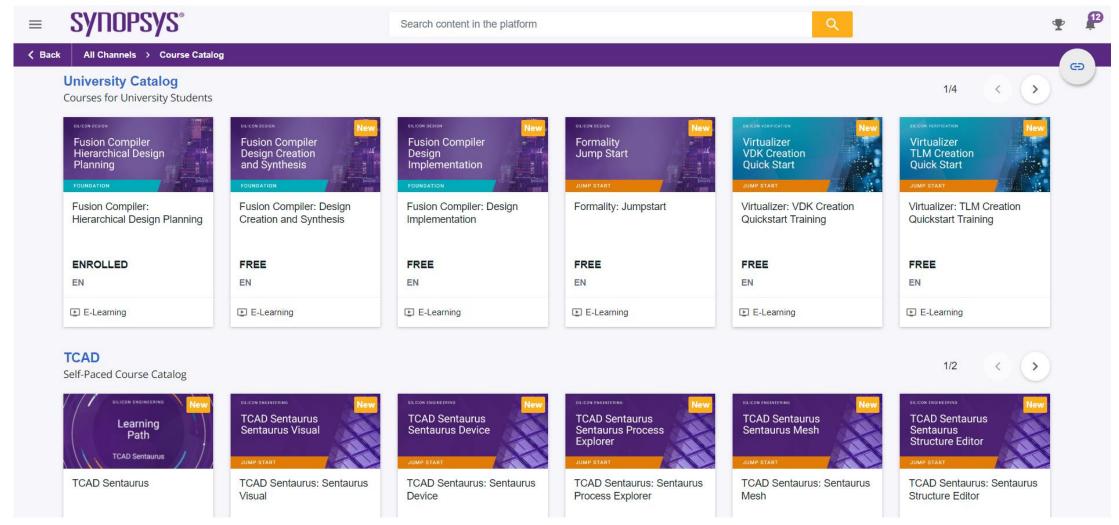

### 04 Click on "Course Catalog"

× SYNOPSYS°

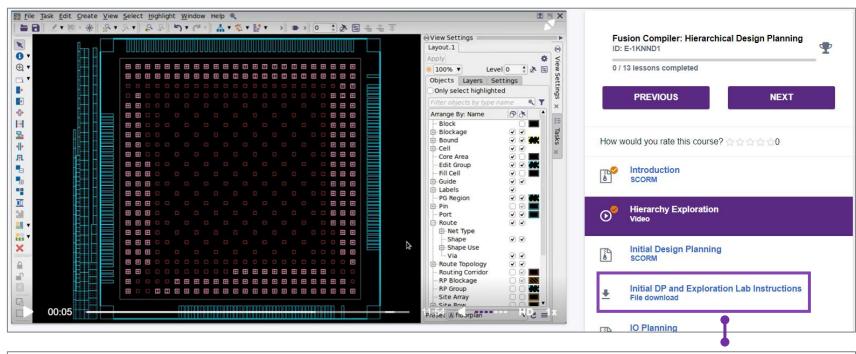

### 05 The Interface of Courses

Menu and transcript are provided.

Scroll down to see course description, including abstract, objectives, audience profile, etc.

Course Description

## Downloadable files/instructions

#### **ABSTRACT**

In this hands-on course, you will use Fusion Compiler or IC Compiler II to create chip and block-level floorplans using a hierarchical (top-down) design planning approach. The focus is on multi-voltage (UPF) system-on-a-chip (SoC) designs with multiple levels of physical hierarchy, which can contain a mix of multiply-instantiated blocks (MIBs), black boxes, and partial netlists.

#### **OBJECTIVES**

At the end of this course you should be able to:

- · Create an NDM design library

- · Read the Verilog outlines

- · Initialize the chip-level floorplan

- · Place the flip-chip bumps

- · Place the Signal IO drivers/pads

- plore the physical design hierarchy

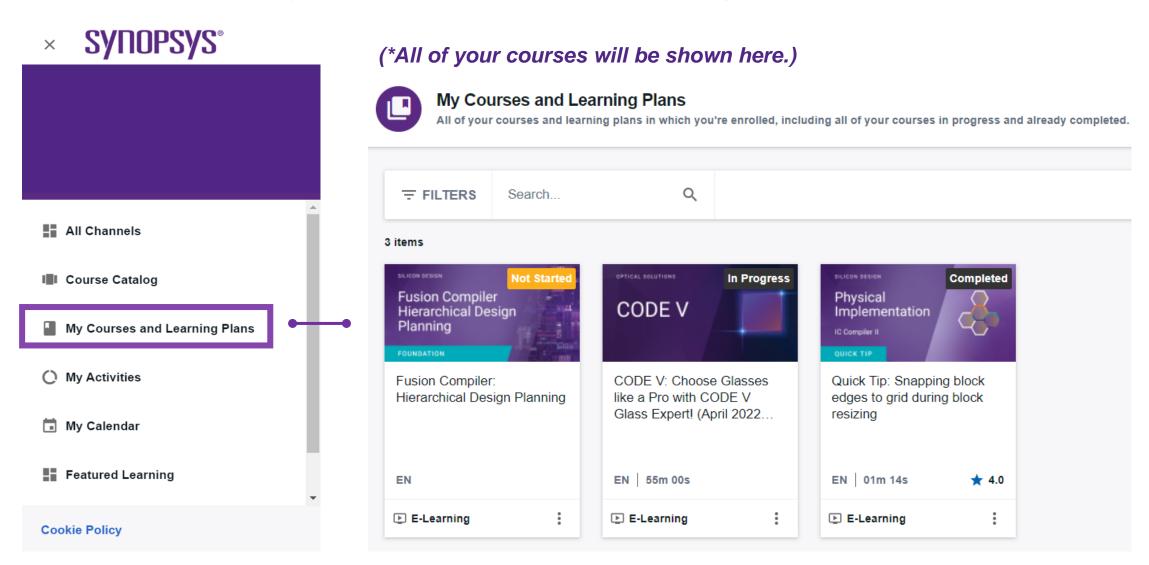

## 06 Click on "My Courses and Learning Plan"

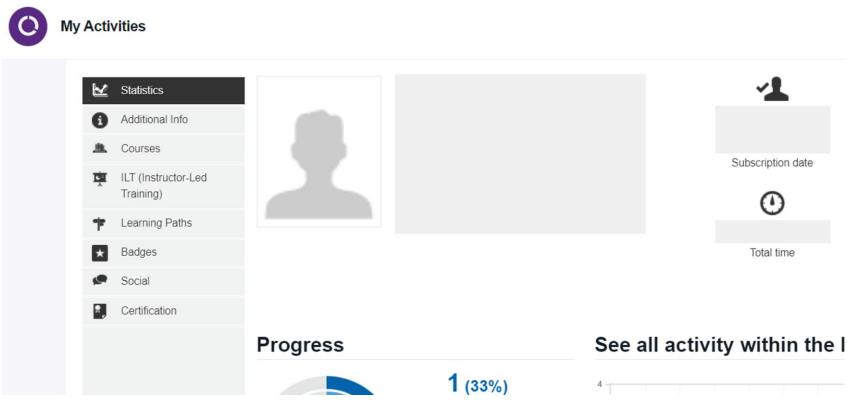

### 07 Click on "My Activities"

SYNOPSYS° All Channels I■I Course Catalog My Courses and Learning Plans My Activities My Calendar Featured Learning **Cookie Policy**

(\*Your information, performance, badges, certification, etc. will be shown here.)

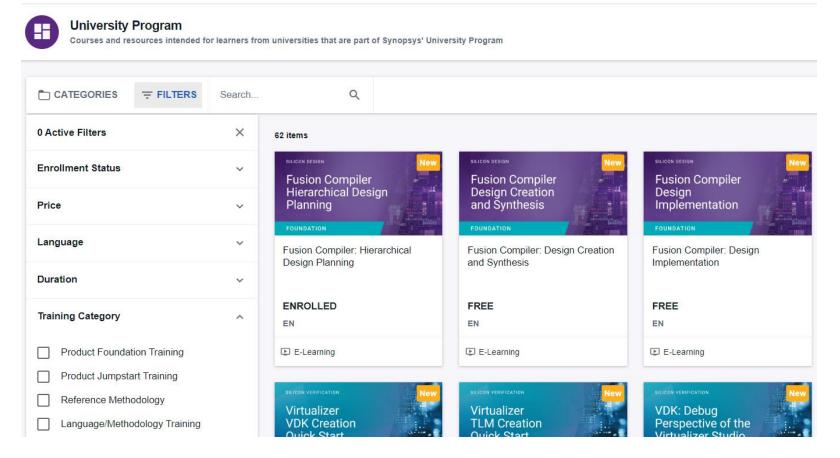

### 08 Click on "University Program"

× SYNOPSYS°

Academic users approved by Synopsys University Program (TW) are entitled to the "Elite" subscription model.

More details for the subscription model (Link).

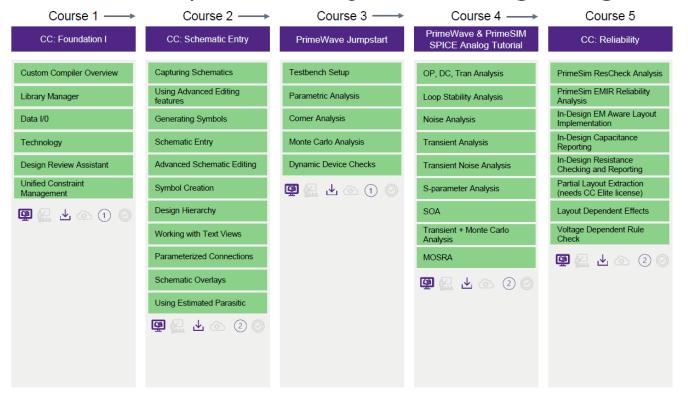

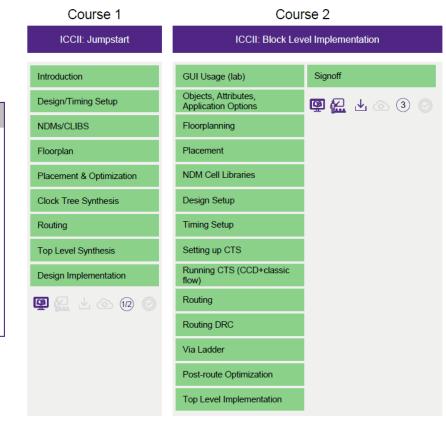

### 09 Synopsys Learning Paths

### Custom Compiler Learning Path Analog Designer

### IC Compiler II Learning Path

Legend

Self-paced

Learning

Instructor-Led

Training

Downloadable Lab

Cloud-based Lab

# Duration in Days

0

Learning Paths are available on Synopsys Learning Center.

-> Explore more Synopsys Learning Paths (Link)

# Thank You

Synopsys University Program

(<a href="mailto:chunhsu@synopsys.com">chunhsu@synopsys.com</a>)