## Unleashing Innovation

ENGINEERING SOLUTIONS FROM SILICON-TO-SYSTEMS

## Powering Innovation Today to Ignite the Ingenuity of Tomorrow

Synopsys delivers the most trusted and comprehensive engineering solutions from silicon to systems, including electronic design automation, silicon IP and systems simulation & analysis, that accelerate technology innovation. We partner closely with semiconductor and systems customers across a wide range of vertical markets to maximize their R&D capability and productivity, powering innovation today that ignites the ingenuity of tomorrow.

In a world where the pace and complexity of innovation is accelerating, the entire silicon to systems ecosystem trusts Synopsys to pioneer new technologies and help them get to market faster, without compromise.

## Driving the Era of Pervasive Intelligence with Engineering Solutions from Silicon-to-Systems

Three major growth drivers are driving engineering solution needs for today and the future. First, the rapid advancement of AI is transforming industries by driving exponential productivity and efficiency gains. Second, the ever-increasing proliferation of silicon content is powering this transformation, from data centers to edge devices, while supporting training and inference. Silicon is at the heart of this revolution. Third, the growing importance of software-defined systems is reshaping the landscape, as software workload needs increasingly dictate overall system and silicon requirements.

Together, these drivers have created the era of pervasive intelligence, where Al and smart technologies are seamlessly integrated into our daily lives, becoming omnipresent and interconnected.

This era is pushing the boundaries of compute performance and energy efficiency, presenting significant challenges. To address these, every aspect of the ecosystem—from system architecture to chip design, software integration, and methodology—must evolve together to improve system efficiency. Advancements in silicon and system design solutions are essential to meet these demands.

## **Artificial Intelligence**

Exponential productivity and efficiency gains Overcoming energy and compute limits

## Silicon Proliferation

More silicon content everywhere Addressing productivity and talent

## **Software-defined Systems**

New applications, new methodologies Enabling increased complexity, enablement of new developers

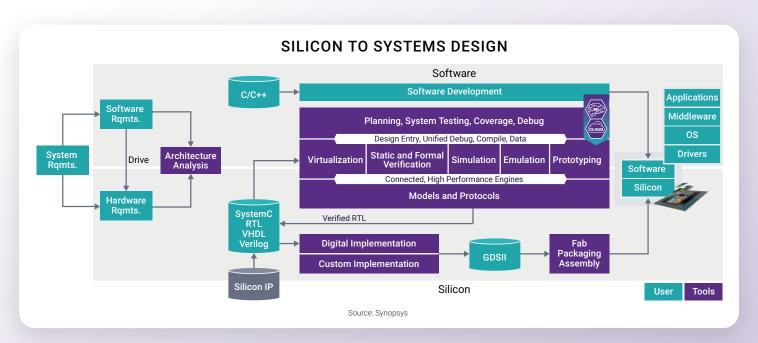

## **Engineering Solutions from Silicon-to-Systems**

Synopsys offers the broadest and most comprehensive array of solutions to enable the design, verification, and implementation of advanced semiconductor chips and electronic systems. These solutions span the entire silicon-to-system spectrum, empowering companies to innovate and bring cutting-edge products to market faster and more efficiently.

### **AI-Driven EDA Suite**

Optimize silicon performance, accelerate chip design and improve efficiency throughout the entire EDA flow with our advanced suite of AI-powered solutions. Award-winning Synopsys.ai™ offers industry leading AI-powered workflow optimization and data analytics solutions along with breakthrough generative AI capabilities, allowing engineers to accelerate innovation and time to market.

## **Multi-Die Design Solution**

Synopsys provides a comprehensive and scalable multi- die solution, including IP and EDA products, from early architecture to manufacturing for fast heterogeneous integration.

### **Accelerate Automotive Innovation**

Synopsys accelerates innovation at automotive OEMs and Tier 1s with silicon to systems design solutions. Synopsys' automotive solution enables hardware/ software co-design to meet E/E, ECU, and SoC architecture requirements and expedites software development and validation with virtual solutions and test automation to reduce time to market while improving software quality.

## **Low-Power Consumer/IoT Solutions**

Optimized solutions for low-power consumer IoT, including energy-efficient silicon IP, advanced design and verification tools, and software development platforms, supports the design of compact, high-performance, and battery-efficient products.

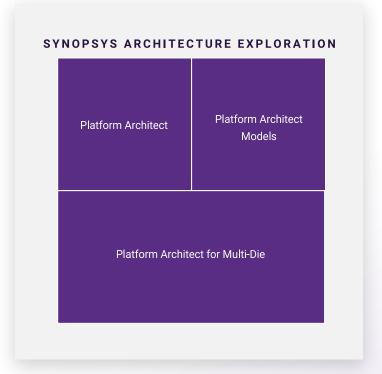

## **Architecture Exploration**

## SoC and Multi-die Architecture Analysis and Optimization for Performance and Power

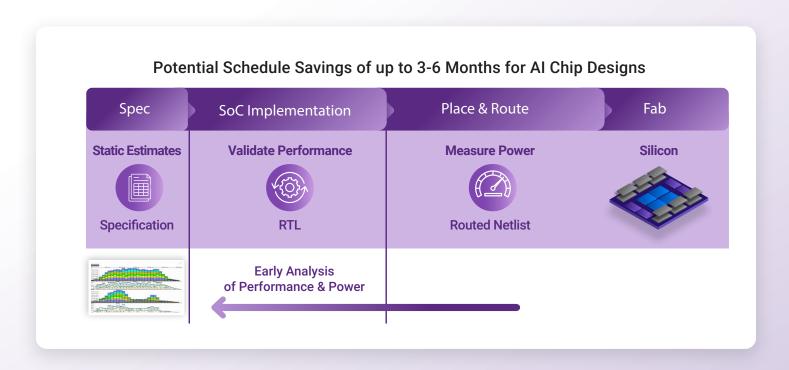

Today's SoC and multi-die complexity means spreadsheet-based architecture tools are inefficient and run a high risk of re-spins to meet power and performance targets, resulting in higher costs and TTM delay. With the largest library of architecture models and fast capture of task and trace-based SW workloads, Platform Architect is the choice to shift-left your architecture design and deliver the right product on schedule.

Synopsys Platform Architect™ is a SystemC™ standards-based performance and power analysis tool for early SoC architecture exploration and design. Using transaction-level simulation, it reduces design time by predicting and optimizing architecture KPIs. Platform Architect helps optimize hardware-software partitioning, IP selection and configuration, interconnect and memory configuration, and power. Platform Architect for Multi-Die accounts for the interdependencies between multiple dies (also referred to as chiplets) within multi-die systems.

## **Digital Design**

## Explore Comprehensively, Implement Convergently, Signoff Confidently

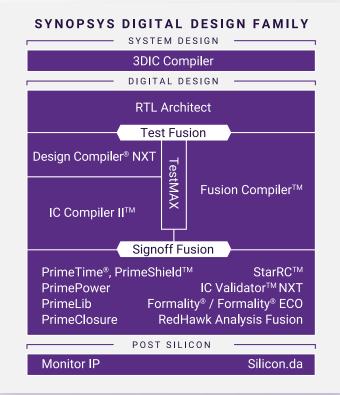

Fusion—bringing together separate elements to create something greater than the sum of the parts—is the defining ethos of the Synopsys Digital Design. Through the unique coalescence of industry-leading technologies and products on a single data model, the Synopsys Digital Design Family allows for an aggressive shift left in design methodology, delivering maximum power, performance, area (PPA) entitlement and significant productivity benefits across the entire RTL-to-signoff flow. Further bolstered by transformative silicon lifecycle management (SLM) technology and the industry's first, unified exploration-to-signoff platform for 2.5D/3D multi-die/advanced package co-design with multiphysics analysis, this transformative solution allows designers to focus less on the mechanics of doing design and instead focus more on the important job of doing innovation.

"The Synopsys team gave us confidence that IC Compiler II place-and-route solution could handle all 1.5 million gates of our design without any issues. The stability of the digital design tools and flows plus the team's support were critical in enabling four engineers to complete this project on our aggressive schedule."

## Vinay N Hebballi Chief Operating Officer

## **DSO.ai™: Al-Driven Design Space Optimization**

Synopsys Al-driven chip design leverages advanced artificial intelligence and machine learning technologies to optimize performance, power, and area, accelerating design cycles and enabling the creation of highly efficient, next-generation semiconductors.

## **Analog & Mixed-Signal Design**

## Virtually Assisted Automation, Faster Analog Design Closure

Analog circuits are the foundation of all electronics and analog circuit design requires a multitude of tools for accurate simulation and analysis of these circuits. The Synopsys Custom Design Family is a unified suite of design and verification tools that accelerates the development of robust analog and mixed-signal designs. The family features Custom Compiler™, a fast, easy-to-use design and layout solution, PrimeSim™ solution which delivers industry-leading circuit simulation performance, and best-in-class technologies for parasitic extraction, reliability analysis, and physical verification.

Synopsys Custom Compiler is a powerful solution for analog and mixed-signal schematic and layout design. It is built on the industry leading custom infrastructure which allows a rich set of functionality and a base to integrate any Synopsys or third-party tool. Combined with the PrimeWave™ Design Environment, designers have an open and flexible simulation setup, waveform viewing and post-processing solution, providing full-cycle design and reliability analysis for analog, RF and mm-wave designs. Synopsys PrimeSim offers a full suite of small-signal and large-signal analog and RF simulation capabilities as well as ML-based High-Sigma Monte Carlo analysis.

- Faster design closure with integrated signoff engines

- World's fastest GPU-accelerated signoff SPICE

- High-sigma Monte Carlo, circuit checks and aging

- Accelerate analog IP design and technology node migration with Al-driven analog design migration

# Custom Compiler™ PrimeSim™ Signoff Fusion NanoTime StarRC™ PrimeLib IC Validator™

## Verification

## Finding Bugs Sooner, Faster and Smarter

The industry's fastest engines are at the core of Synopsys' verification family, enabling comprehensive verification of entire SoCs with the industry-leading VCS® simulation, Verdi® debug, VC SpyGlass™ static analysis, VC Formal™, and silicon-proven Verification IP. The unified compile feature with VCS ensures a seamless transition between static, formal, simulation, emulation, and prototyping environments, enhancing workflow efficiency. Synopsys VSO.ai™ (Verification Space Optimization) delivers the industry's first Al-driven verification solution to help verification teams find bugs faster and achieve coverage closure faster, with higher quality. Additionally, unified debugging with the next-gen Verdi platform enables design visualization and resolution of bugs across all domains and abstraction levels, significantly boosting debug efficiency. Native integrations further enhance verification productivity, performance, and throughput, making Synopsys' solutions a powerful choice for advanced verification needs.

## SYNOPSYS VERIFICATION FAMILY

| Planning & Coverage                       |                                  |      |       |       |  |  |

|-------------------------------------------|----------------------------------|------|-------|-------|--|--|

| Verdi®                                    |                                  |      |       |       |  |  |

| Platform<br>Architect™<br>Visualizer™     | VC<br>SpyGlass™<br>VC<br>Formal™ | VCS® | ZeBu® | HAPS® |  |  |

| VIP, Transactors, Virtual & Memory Models |                                  |      |       |       |  |  |

|                                           |                                  |      |       |       |  |  |

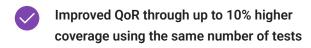

## Renesas' Compelling Results with VSO.ai

Reduced coverage holes by 90%

"Implementing Synopsys VCS ICO into our flow helped us to reveal hard-to-detect bugs with a significantly reduced number of simulation seeds. The ability to detect these elusive bugs earlier and with fewer tests has not only improved our efficiency but also enhanced the quality of our final product."

## **Uda Kothapalli**

Verification Engineer, Microsoft

Microsoft

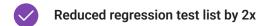

## Silicon Lifecycle Management & Test Automation

## Actionable Insights Through Silicon Lifecycle Monitoring, Analytics, and Advanced Test Capabilities

Semiconductor design, manufacturing and system deployment are challenged on many fronts due to process variability, device aging effects, ever increasing performance expectations, and the continued reduction in time to volume. Synopsys is leading the industry to solve these challenges with its Silicon Lifecycle Management (SLM) solution, a comprehensive set of integrated tools, IP and methodologies. SLM intelligently and efficiently collects and stores monitor data throughout a system's life and provides actionable insights through the use of powerful analytics.

Synopsys TestMAX™ and SMS IP offer a powerful and highly configurable test automation flow with seamless integration of all Synopsys test capabilities. Early validation of complex DFT logic is supported through full RTL analysis and integration while maintaining physical, timing and power awareness through direct value links into the Synopsys Digital Design Family. These features, combined with comprehensive support for early testability analysis and planning, Al-driven test optimization, hierarchical ATPG compression, physically aware diagnosis, logic BIST, memory self-test and repair and pattern translation, ensure the Synopsys TestMAX and SMS IP family address critical test issues and enables effective test for the most demanding applications.

| SYNOPSYS TEST FAMILY    |                        |                             |  |  |

|-------------------------|------------------------|-----------------------------|--|--|

| Synopsys Digital Design |                        |                             |  |  |

| TestMAX<br>Advisor      | TestMAX<br>DFT         | TestMAX<br>ATPG             |  |  |

| SMS/<br>SHS IP          | TestMAX<br>Manager     | TestMAX<br>XLBIST           |  |  |

| TestMAX<br>Diagnosis    | TestMAX<br>Vtran       | TestMAX<br>ALE &<br>HSAT IP |  |  |

| TSO.ai                  | (Al-driven Test Optimi | zation)                     |  |  |

"Multiple design groups from Socionext and Synopsys collaborated as a cross-functional team to satisfy the design for test (DTF) requirements on a challenging multi-die system-on-chip (SoC) project with a master die chiplet and four High Bandwidth memory (HBM) modules. We completed all DTF items and successfully shipped the product on schedule, at the target data rate, and without any impact on logic die size."

## Shinichiro Ikeda

Senior Principal Engineer, Socionext Inc.

socionext

## **Design Signoff**

## Trusted, Unified Signoff Solution for Leading-Edge Chip Designs

Synopsys' design analysis and signoff solutions accelerate design closure through a unified environment that delivers hyperconvergence to drive first-pass silicon success while optimizing power, performance, and area. Synopsys signoff solutions ensure a chip design meets all functional, performance, and manufacturability requirements before fabrication. Synopsys signoff encompasses several key components, including timing signoff, which ensures the design meets timing constraints across all process, voltage, and temperature (PVT) corners using tools like Synopsys PrimeTime® for static timing analysis (STA). Power signoff validates power consumption targets and power integrity with tools like PrimePower, while signal integrity signoff addresses issues such as crosstalk, electromigration, and IR drop using in-design analysis. Physical verification ensures adherence to manufacturing rules through design rule checks (DRC) and layout vs. schematic (LVS) checks using tools like IC Validator. Reliability signoff ensures the design is robust over its lifetime, addressing aging, thermal effects, and electromigration with tools like PrimeSim™ or HSPICE®. Additionally, functional verification ensures the design behaves as intended under all scenarios using tools like Synopsys VCS simulation or Formality<sup>®</sup>. This comprehensive process is essential for ensuring fabrication readiness, meeting performance targets, and mitigating risks, ultimately enabling high-quality, manufacturable designs.

## SYNOPSYS SIGNOFF ANALYSIS

| PrimeTime<br>PrimeShield™<br>PrimeClosure<br>Timing Constraints<br>Manager | PrimePower<br>PrimePower RTL<br>ZeBu® Empower |

|----------------------------------------------------------------------------|-----------------------------------------------|

| StarRC™<br>IC Validator™                                                   | PrimeLib<br>NanoTime<br>ESP                   |

- Trusted on the world's most advanced tapeouts

- Highest-performance timing, power, extraction and characterization engines

- Innovation leader in ECO, robustness, and constraints for design closure & PPA

## **Manufacturing & TCAD**

## **Powering Innovation, Maximizing Efficiency**

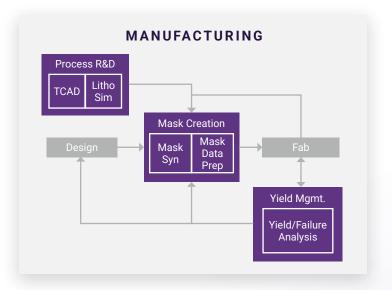

Synopsys' manufacturing solutions deliver a competitive edge by providing an end-to-end suite of tools that streamline the design-to-silicon process and tackle the challenges of advanced nodes, including multi-patterning, EUV lithography, and complex design rules. With strong foundry partnerships, a proven track record, and world-class customer support, these solutions ensure first-pass success and empower semiconductor companies to innovate, reduce costs, and accelerate time to market with confidence.

- Mask Solutions: Synopsys Proteus™ for mask synthesis, S-Litho for lithography simulation, and S-Metro for metrology ensure high accuracy and performance, while Mask Data Prep optimizes the mask data workflow to enable precision and manufacturability. Together, these solutions address the complexities of advanced mask manufacturing with scalability, accuracy, and seamless integration into lithography workflows.

- Manufacturing Analytics: Synopsys' Process and Product analytics solutions help identify and resolve yield-limiting factors early, enabling faster ramp-up and efficient high-volume manufacturing. These tools provide actionable insights to optimize production and improve overall yield.

- Platform for semiconductor process and device simulation. By combining advanced physics models, multi-scale simulation capabilities, and seamless integration with EDA tools, Synopsys Sentaurus™ and QuantumATK® empower engineers and researchers to tackle the challenges of modern semiconductor design and manufacturing.

## **NEWS RELEASE**

TSMC and Synopsys Bring Breakthrough NVIDIA Computational Lithography Platform to Production

"Computational lithography is a cornerstone of chip manufacturing," said Jensen Huang, founder and CEO of NVIDIA. "Our work on cuLitho, in partnership with TSMC and Synopsys, applies accelerated computing and generative AI to open new frontiers for semiconductor scaling."

"For more than two decades Synopsys

Proteus mask synthesis software products

have been the production-proven choice for

accelerating computational lithography—the

most demanding workload in semiconductor

manufacturing," said Sassine Ghazi, president

and CEO of Synopsys. "Our collaboration

with TSMC and NVIDIA is critical to enabling

angstrom-level scaling as we pioneer advanced

technologies to reduce turnaround time by

orders of magnitude through the power of

accelerated computing."

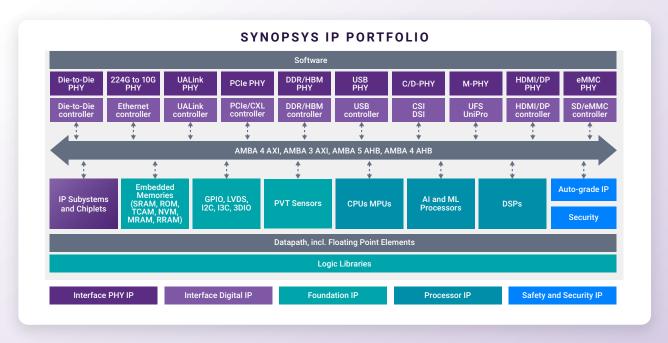

## Silicon IP

Reduce integration risk and speed time-to-market with best-in-class, silicon-proven IP

Synopsys IP accelerates product development, enhances performance, and reduces design risk for complex chips and systems, allowing designers to focus on their competitive differentiation. By selecting Synopsys IP, organizations can access a comprehensive portfolio of pre-verified, high-quality IP blocks. This significantly reduces the time and effort required for in-house development, enabling faster time-to-market for products. Synopsys IP is designed to meet industry standards and is optimized for performance, power efficiency, and area, providing seamless integration.

Each Synopsys IP solution undergoes rigorous testing and validation to ensure compliance with the latest protocols and specifications, helping to minimize design errors and elevate product quality. By integrating Synopsys IP, organizations can concentrate on their core strengths while benefiting from trusted, industry-leading technology to streamline development and achieve superior results.

Leader in Interface IP

Leader in Foundation IP

#2 IP provider worldwide

25 years of investment & commitment

"As a lean startup, we don't have the bandwidth to design all the IP ourselves or to entertain multiple vendors. We needed a single supplier for proven IP, from computer vision to PCI Express, Ethernet, MIPI CSI-2, memory interfaces, I2C, UARTs, security. Synopsys has it all."

## Srivi Dhruvanarayan

VP of Silicon Engineering, SiMa.ai

💥 SiMa

## Silicon IP

Synopsys offers a comprehensive IP portfolio that spans logic library IP, embedded memory IP, interface IP, security IP, embedded processors, and subsystems, supporting a wide variety of application domains and industry requirements. Designed to be compatible with leading foundries, this portfolio ensures smooth integration across multiple manufacturing processes and allows customers to adopt the latest process technologies for enhanced performance and efficiency. The portfolio also addresses specialized needs, such as automotive- grade IP that meets rigorous reliability, safety, and quality standards—including support for ISO 26262—and robust security IP featuring advanced encryption, authentication, and hardware root-of-trust for data protection.

To accelerate IP integration and silicon bring-up, Synopsys' IP Accelerated initiative delivers architecture design expertise, IP hardening, and comprehensive signal and power integrity analysis. This approach helps customers integrate IP quickly and efficiently, reducing the complexity of design and minimizing development cycles. Synopsys' ongoing investment in IP quality, combined with thorough technical support and a proven IP development methodology, empowers designers to reduce integration risk and achieve faster time-to-market—whether they are addressing high-speed interfaces, memory, logic, connectivity, or embedded processors. With detailed documentation, global support, and regular updates, Synopsys enables organizations to confidently innovate and meet the demands of next-generation designs.

"With our longstanding collaboration with Synopsys and our integration of Synopsys Controller and PHY IP, including PCIe, MIPI, and Ethernet, into our automotive chips, we are delivering the intelligence and connectivity that are defining the automotive world."

## Dr. Jörg Schepers

VP Automotive Microcontrollers, Infineon

## **Hardware-Assisted Verification**

## Hardware-Assisted Verification is Critical to Silicon Success

Compounding complexities—spanning software, hardware, interfaces, and workload-optimized architectures—are creating tremendous challenges for those developing today's most advanced chip, system on chip (SoC), and multi-die designs. Verification and software development processes, in particular, can require quadrillions of test and validation cycles across simulation, emulation, and prototyping stages. As a result, there has been a distinct need for faster hardware-assisted verification (HAV) solutions that accelerate the development and validation of advanced chip designs and help ensure optimized functionality of the software-defined systems they enable. Synopsys ZeBu® and HAPS® systems are advanced emulation and prototyping solutions for HAV that offer significant benefits for semiconductor design and verification. HAPS provides high-performance prototyping capabilities, enabling early software development, system validation, and hardware-software integration, which accelerates time- to-market. ZeBu delivers high-performance emulation, allowing for thorough verification of complex SoC designs with extensive debug capabilities. Together, these tools enhance productivity by enabling parallel hardware and software development, reducing risks associated with late- stage design changes, and improving overall design quality and reliability. Their comprehensive support for various use cases including RTL verification and regressions, architecture, performance and low power optimization, software bring-up, and regressions and compliance verification ensure seamless integration and efficient project execution.

## **Key Benefits**

- Improved System & Product

Quality—Ensure efficient, correct system

function in real-world applications

- Accelerated Time-to-Market—Faster execution of verification tasks

- Reduction of Costly Silicon

Respins—Identify and fix issues early,

minimizing costly silicon respins

"Rebellions' partnership with Synopsys and integration of VCS, ZeBu and Virtualizer has allowed us to excel in innovating AI hardware, navigate chip design complexity, and meet global IT market demands. Leveraging Synopsys' cutting-edge emulation technology, Rebellions has enhanced performance, increased reliability, and accelerated market readiness."

### Jinwook Oh

Co-founder and CTO, Rebellions

rebellions

## **Early Software Development**

## Accelerate Innovation with Earlier and Faster Software Development

The integration of increasingly complex hardware and software is a significant challenge for semiconductor and OEM companies developing next-generation wireless, consumer and automotive devices. Traditional methods of serialized hardware and software development, where the vast majority of software is developed and verified after the silicon design is complete, often fail to meet aggressive product development schedules.

Software development and validation using virtual prototype results in faster time-to-market through earlier and faster software development and improved communication throughout the supply chain. Software engineers can start development months before the hardware design is complete, enabling full system bring- up to occur within days of silicon availability. Virtual prototypes are fast, fully functional software models of complete systems that execute unmodified production code and provide unparalleled debug efficiency. Synopsys' solutions play a crucial role in the development process by allowing engineers to develop, test, and validate each step before production, from SoC to ECU to E/E Architecture. This ensures that potential issues are addressed early, optimizing the design for performance, safety, reliability, quality, and security.

## **Key Benefits of Virtual Prototyping**

**Embedded Software Development**

Start before hardware is available (even pre-RTL)

**Optimized Implementation**

Semiconductor and electronics companies enabled by Synopsys tools, methodologies and services

**Increased Productivity**

Powerful debug and analysis tools boost developers, test and verification team efficiency

**Easy Deployment**

Enhanced communication enabling suppliers and customers' concurrent development

## SYNOPSYS VIRTUAL PROTOTYPING

| Silver                                               | Virtualizer |

|------------------------------------------------------|-------------|

| Automotive Virtualizer<br>Development Kits<br>(VDKs) | ТРТ         |

## SYNOPSYS®

Synopsys is the leader in engineering solutions from silicon to systems, enabling customers to rapidly innovate Al-powered products. We deliver industry-leading silicon design, IP, simulation and analysis solutions, and design services. We partner closely with our customers across a wide range of industries to maximize their R&D capability and productivity, powering innovation today that ignites the ingenuity of tomorrow.

Learn more at www.synopsys.com

©2025 Synopsys, Inc. All rights reserved. Synopsys is a trademark of Synopsys, Inc. in the United States and other countries. A list of Synopsys trademarks is available at <a href="http://www.synopsys.com/copyright.html">http://www.synopsys.com/copyright.html</a>. All other names mentioned herein are trademarks or registered trademarks of their respective owners.