#### **SYNOPSYS**<sup>®</sup>

#### Synopsys Learning Journeys An easy access guide to your learning

### CONFIDENTIAL INFORMATION

The information contained in this presentation is the confidential and proprietary information of Synopsys. You are not permitted to disseminate or use any of the information provided to you in this presentation outside of Synopsys without prior written authorization.

#### IMPORTANT NOTICE

In the event information in this presentation reflects Synopsys' future plans, such plans are as of the date of this presentation and are subject to change. Synopsys is not obligated to update this presentation or develop the products with the features and functionality discussed in this presentation. Additionally, Synopsys' services and products may only be offered and purchased pursuant to an authorized quote and purchase order or a mutually agreed upon written contract with Synopsys.

# Table of Contents

#### **Product-based Journeys**

- <u>Custom Compiler</u>

- Design Compiler NXT

- <u>DSO.ai</u>

- <u>ESP</u>

- Formality

- Fusion Compiler

- <u>FC/ICC II Hierarchical Design Planning</u>

- <u>Fusion Platform Methodology</u>

- <u>HAPS</u>

- IC Compiler II

- IC Validator

- Library Compiler

- Language

- LynxNXT

- <u>PrimeLib</u>

- PrimePower

- PrimeSim

- PrimeTime

- <u>Reference Methodology</u>

- RTL Architect

- <u>SaberRD</u>

- <u>Synplify</u>

- <u>StarRC</u>

- <u>TestMAX Advisor</u>

- <u>TestMAX Access</u>

- <u>TestMAX FuSa</u>

- <u>TestMAX Manager</u>

- <u>TestMAX SMS</u>

- <u>TestMAX XLBIST</u>

- <u>Tweaker</u>

- VC Formal

- <u>ZeBu</u>

#### **Role-based Journeys**

- Analog Designer

- <u>RF/Transceiver Designer</u>

- Digital Designer

- Physical Designer

| Custom                           |                                     | earning Pat           | II Analog I                                   | Jesigner                                              |

|----------------------------------|-------------------------------------|-----------------------|-----------------------------------------------|-------------------------------------------------------|

| Course 1>                        | Course 2>                           | Course 3>             | Course 4>                                     | Course 5                                              |

| Custom Compiler:<br>Foundation I | Custom Compiler:<br>Schematic Entry | PrimeWave Jumpstart   | PrimeWave & PrimeSIM<br>SPICE Analog Tutorial | Custom Compiler:<br>Reliability                       |

| Custom Compiler Overview         | Capturing Schematics                | Testbench Setup       | OP, DC, Tran Analysis                         | PrimeSim ResCheck Analysis                            |

| Library Manager                  | Using Advanced Editing<br>features  | Parametric Analysis   | Loop Stability Analysis                       | PrimeSim EMIR Reliability<br>Analysis                 |

| Data I/0                         | Generating Symbols                  | Corner Analysis       | Noise Analysis                                | In-Design EM Aware Layout<br>Implementation           |

| Technology                       | Schematic Entry                     | Monte Carlo Analysis  | Transient Analysis                            | In-Design Capacitance<br>Reporting                    |

| Design Review Assistant          | Advanced Schematic Editing          | Dynamic Device Checks | Transient Noise Analysis                      | In-Design Resistance<br>Checking and Reporting        |

| Unified Constraint<br>Management | Symbol Creation                     |                       | S-parameter Analysis                          | Partial Layout Extraction<br>(needs CC Elite license) |

|                                  | Design Hierarchy                    |                       | SOA                                           | Layout Dependent Effects                              |

|                                  | Working with Text Views             |                       | Transient + Monte Carlo<br>Analysis           | Voltage Dependent Rule<br>Check                       |

|                                  | Parameterized Connections           |                       | MOSRA                                         |                                                       |

|                                  | Schematic Overlays                  |                       |                                               |                                                       |

|                                  | Using Estimated Parasitic           |                       |                                               |                                                       |

|                                  |                                     |                       |                                               |                                                       |

|                                  |                                     |                       |                                               |                                                       |

| 👰 🛴 🛃 🙆 1) 🔘                     | ፼ ፼ ↓ 		 2                          | ፼ 🔬 🛃 💿 (1 ) ⊘        | 🚇 🔬 🛃 🙆 🔍 🔘                                   | 🚇 🔬 🛃 💿 😢 🔘                                           |

#### Custom Compiler Learning Path Analog Designer

SYNOPSYS®

Synopsys Confidential Information

Badge

4

Legend

Self-paced Learning

Instructor-Led Training Downloadable Lab Cloud-based Lab (#) Duration in Days пΪ

## Custom Compiler Learning Path RF/Transceiver Designer

----> Course 6

Custom Compiler : ICC2 CoDesign

**Data Preparation**

Analog BlackBox Preparation

**Digital Implementation**

ICC2 Editing

Capacitance Reporting and Checking

Legend Self-paced Learning لم هفه Instructor-Led Training ,√, Downloadable Lab 6 Cloud-based Lab # Duration in Days (~ Badge

П

### Design Compiler NXT Learning Path

| Course 1                          | Course 2                                       | Course 3                                        | Course 4>                              | Course 5                                                |

|-----------------------------------|------------------------------------------------|-------------------------------------------------|----------------------------------------|---------------------------------------------------------|

| Design Compiler NXT:<br>Jumpstart | Design Compiler NXT :<br>RTL Synthesis         | Design Compiler NXT :<br>Clock Gating Low Power | Design Compiler NXT :<br>DFT Insertion | Design Compiler NXT:<br>SystemVerilog for RTL<br>Design |

| Introduction                      | Introduction to DC NXT                         | Introduction                                    | Introduction                           | Introduction                                            |

| Design Setup                      | Design Setup for Physical<br>Synthesis         | Power Analysis                                  | Scan Testing and Flows                 | SystemVerilog Features                                  |

| Reading RTL Design                | Accessing Design and Library<br>Object         | Power Optimization                              | Test Protocol                          | Implementing User Logic<br>Intent                       |

| Loading Floorplan Data            | Constraints: Reg-to-Reg and I/O Timing         | Clock Gating                                    | DFT Design Rule Checks                 | Combinational Logic/Latches                             |

| Constraining Design               | Advanced Schematic Editing                     | Advanced Clock Gating                           | DFT DRC GUI Debug                      | Meaning of full/parallel                                |

| Synthesis Techniques              | Input Transition and Output<br>Loading         | Self Gating                                     | DRC Fixing                             | Registers                                               |

| Post Synthesis Outputs            | DC NXT Ultra Synthesis<br>Techniques           | Multibit                                        | Top-Down Scan Insertion                | State Machine                                           |

|                                   | Timing Analysis                                | ICC II Link                                     | Advanced Scan Insertion                | Wildcard & Tri-state logic                              |

|                                   | Constraints: Multiple Clocks<br>and Exceptions | Reporting                                       | Bottom-up Scan Insertion               | Pack/Unpack Array &<br>Struct/Union                     |

|                                   | SPG Flow, Congestion,<br>Layout GUI            |                                                 | Export                                 | Interface & Package                                     |

|                                   | Constraints: Complex Design<br>Considerations  |                                                 | On-Chip Clocking (OCC)                 | Achieving High QoR-Coding                               |

|                                   | Post-Synthesis Output Data                     |                                                 | DFTMAX                                 |                                                         |

|                                   | Clk Gating/Leakage<br>Power analysis           |                                                 | Advanced Topics                        |                                                         |

| 🚇 📊 占 💿 112 🎯                     | 🚇 🔬 🕹 🙆 🕥                                      | 🚇 🔂 🕹 💿 🌖 🔘                                     | 🚇 🚛 🕹 💿 📀 🔘                            |                                                         |

Legend Self-paced Learning Learni ۲Ţ

####

### Recommended Learning Journey for a Digital Designer

| Course 1>                               | Course 2>                                      | Course 3>                                       | Course 4                                  | Course 5                          | 4                                |

|-----------------------------------------|------------------------------------------------|-------------------------------------------------|-------------------------------------------|-----------------------------------|----------------------------------|

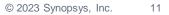

| Library Compiler:<br>Foundation         | Design Compiler NXT:<br>Synthesis              | Fusion Compiler: Design<br>Creation & Synthesis | Fusion Compiler: Design<br>Implementation | Fusion Compiler: DFT<br>Insertion |                                  |

| Introduction                            | Introduction to DC NXT                         | Introduction & GUI                              | Floorplanning                             | Introduction                      |                                  |

| Functional Modeling                     | Design Setup for Physical Synthesis            | Reading RTL                                     | Setting up CTS                            | Scan Testing and Flows            |                                  |

| Timing Modeling                         | Accessing Design and Library Object            | Objects, Attributes,<br>Application Options     | Running CTS (CCD & Classic<br>Flow)       | Test Protocol                     |                                  |

| Low Power Modeling                      | Constraints: Reg-to-Reg and I/O Timing         | Compile Flows and Setup                         | Routing                                   | DFT Design Rule Checks            |                                  |

| Modeling for Test                       | Advanced Schematic Editing                     | NDM Cell Libraries                              | Routing DRC                               | DFT DRC GUI Debug                 | Legend                           |

| Library Creation Guidelines             | Input Transition and Output<br>Loading         | Loading UPF and Floorplan                       | Via Ladder                                | DRC Fixing                        | Self-paced                       |

| CCS Modeling                            | DC NXT Ultra Synthesis<br>Techniques           | Timing Setup & OCV                              | Post-route Optimization                   | Top-Down Scan Insertion           | Self-paced<br>Learning           |

| OCV Modeling                            | Timing Analysis                                | CCD Optimization                                | Signoff                                   | Advanced Scan Insertion           |                                  |

| Check Library                           | Constraints: Multiple Clocks<br>and Exceptions | Power Optimization                              |                                           | Bottom-up Scan Insertion          | Instructor-Led<br>Training<br>↓↓ |

| Advance Node Features                   | SPG Flow, Congestion,<br>Layout GUI            | Additional Compile Settings<br>and Techniques   |                                           | Export                            | Downloadable<br>Lab              |

| Library Analytics                       | Constraints: Complex Design<br>Considerations  |                                                 |                                           | On-Chip Clocking (OCC)            | Cloud-based Lab                  |

| Physical Library Preparation & Creation | Post-Synthesis Output Data                     |                                                 |                                           | DFTMAX                            | (#)                              |

| Fusion Library Creation                 | Clock Gating/Leakage<br>Power Analysis         |                                                 |                                           | Advanced Topics                   | Duration in Days                 |

| 👰 🛴 🕹 🙆 🔘                               |                                                | 🚇 🔛 🕁 💿 🌖 🔘                                     | 👰 🔛 🕁 💿 📀 🔘                               | 🚇 🚰 🕹 🙆 📀 🔘                       | Badge                            |

Synopsys Confidential Information

#### Recommended Learning Journey for a Digital Designer

| Course 6                                | Course 7>                                     | Course 8                    | Course 9                                  |

|-----------------------------------------|-----------------------------------------------|-----------------------------|-------------------------------------------|

| Fusion Compiler: SOC<br>Design Planning | Prime Time: Foundation                        | StarRC: Foundation          | IC Validator: User<br>(DRC & LVS)         |

| Initial Design Planning                 | Introduction to STA in<br>PrimeTime           | Extraction Fundamentals     | Setup ICV and Run DRC/LVS<br>Testcase     |

| IO Planning                             | STA Concepts and Flow in<br>PrimeTime         | Gate Level Extraction       | DRC Error Classification                  |

| From Commit to Abstract<br>Creation     | Methodology: Qualifying<br>Constraints        | Transistor Level Extraction | Execute DRC Testcase with Select Commands |

| VA and Block Shaping                    | Methodology: Generating<br>Reports            | Selective Netlist           | LVL                                       |

| Macro Placement                         | Constraining Multiple Clocks                  | Field Solver                | Text Options                              |

| PG PPNS                                 | Additional Checks and<br>Constraints          | Process Modelling           | Generate ICV formatted netlist            |

| Pin Placement                           | Correlation: POCV and AWP<br>Analysis         | Metal Fills                 | Generate Equivalence<br>Options           |

| Timing and Budgeting                    | Signoff: Path Based Analysis (PBA)            |                             | Debug LVS Errors                          |

| Integration/Assembly                    | Signal Integrity: Crosstalk<br>Delay Analysis |                             | Using Short Finder                        |

|                                         | Signal Integrity: Crosstalk<br>Noise Analysis |                             |                                           |

|                                         | Timing Closure: ECO/What If<br>Analysis       |                             |                                           |

|                                         | Large Data: DMSA and<br>Hyperscale Analysis   |                             |                                           |

|                                         |                                               |                             |                                           |

|                                         | 🗐 🚛 🕁 💿 (3) 🔘                                 |                             | 🚇 🚰 🕁 💿 2 🔘                               |

Synopsys Confidential Information

### Recommended Learning Journey for a Digital Designer

| Course 10                                 |                                            | Course 11                           | Course 12                                 |

|-------------------------------------------|--------------------------------------------|-------------------------------------|-------------------------------------------|

| IC Validator: Runset                      |                                            | Reference Methodology:<br>Jumpstart | Fusion Platform<br>Methodology: Jumpstart |

| Overview                                  | Compare                                    | Introduction & Overview             | Introduction & Overview                   |

| Language Introduction                     | Benefits of New Language                   | Organization & Structure            | Organization & Structure                  |

| Command API                               | PXL Compare Syntax<br>Strategy             | Running RM                          | Lab Example                               |

| Writing a Simple "Flat" Rule<br>Runset    | Anatomy of Compare<br>Functions            | Demo                                | Installation & Setup                      |

| Running a Simple IC<br>Validator Runset   | Complementary Compare<br>Functions         |                                     | FCRM for FPM Users                        |

| Advanced Programming<br>Concepts          | User-defined Functions                     |                                     | FAQ – Common Topics                       |

| IC Validator API Header<br>Files          | StarRC Transistor-level<br>Extraction Flow |                                     |                                           |

| Runset Coding Practices                   |                                            |                                     |                                           |

| Layout Device Extraction                  |                                            |                                     |                                           |

| Benefits of New Language                  |                                            |                                     |                                           |

| Runset Structure                          |                                            |                                     |                                           |

| Anatomy of Device Extraction<br>Functions |                                            |                                     |                                           |

| Property Calculation                      |                                            |                                     |                                           |

| User-defined Property<br>Functions        | 🚇 🚰 난 💿 ③ ⊘                                | 👰 掘 날 💿 🕡 🔘                         | 👰 🛴 占 🙆 🕖 🔘                               |

Synopsys Confidential Information

#### Custom Compiler Learning Path RF/Transceiver Designer Course 1 -----Course 2 -----Course 3 -----> Course 4 — Course 5 Custom Compiler: **Custom Compiler:** Custom Compiler: Basic **Custom Compiler: Custom Compiler:** Accelerated Layout Layout Design Reliability Automated Layout Design Foundation I Decian Schematic Driven Lavout **Custom Compiler Overview** Layout Design Entry **Placement Assistant** PrimeSim ResCheck Analysis (SDL) Initialization **Abutment & Align Functions** SDL Placement with PrimeSim EMIR Reliability Library Manager **Pin Placer Advanced Editing Functions Connectivity Use** Analysis SDL ECO & Cross Object In-Design EM Aware Layout Data I/0 **Hierarchical Design Creation Block Placer** Referencing Implementation In-Design Capacitance **Connectivity Engine Placement Advanced** Technology Router Introduction Reporting In-Design Resistance **Design Review Assistant** Abstract Generation Symbolic Editor Pattern Router Legend Checking and Reporting Unified Constraint Partial Layout Extraction Visually Assisted Automation Design Rule Aware Editing Interactive Router Management (needs CC Elite license) Self-paced **Template Manager** Mcell Guard Ring Layout Dependent Effects Auto Router Learning ر م Voltage Dependent Rule Advanced Node Support Shielding Check Instructor-Led Multi Pattern Technology Training Scripting ,√, User Defined Devices (UDD) Antenna Rule Support Downloadable Lab **Physical Verification** 6 **Technology Enablement** Cloud-based Lab **Parasitic Extraction** # Duration in Days $\langle \mathcal{N} \rangle$ Badge

#### synopsys°

Synopsys Confidential Information

{⊘}

Badge

Legend

Self-paced Learning

Instructor-Led Training United Training United Training United Training Downloadable Lab Cloud-based Lab (#) Duration in Days  $\widehat{\mathbb{A}}$

#### DSO.ai Learning Path

Course 1

**DSO:** Foundation

Introduction

Cold Start

Warm Start

👰 🔐 上 🙆 112 🔘

### **ESP** Learning Path

Course 1

ESP: Jumpstart

Introduction

Symbolic Simulations

**Functional Accuracy**

**PIV Introduction**

' L

| SYNO | PSYS <sup>®</sup> |

|------|-------------------|

|------|-------------------|

# Formality Learning Path

|                        | Course 2                              |

|------------------------|---------------------------------------|

| Formality: Jumpstart   | Formality: Foundation                 |

|                        |                                       |

| Overview               | Introduction to Equivalency checking  |

| SVF Guidance           | Concept & Step                        |

| Design Read            | Simple Logic Cones & Failing Points   |

| Setup for Verification | Multi-Stage Verification & SVF        |

| Match and Verify       | Multi-Voltage Designs & UPF           |

| Debugging              | Hard Verifications & SVP              |

| Formality Lab          | Efficient Debugging                   |

|                        | RTL & Netlist Interpretation          |

|                        | Sequential Design<br>Transforms & SVF |

|                        | Other Design Transforms & SVF         |

|                        | Conclusion                            |

|                        |                                       |

### Fusion Compiler Learning Path

| Course 1                               | Course 2                                        | Course 3                                  | Course 4                          | Course 5                  |

|----------------------------------------|-------------------------------------------------|-------------------------------------------|-----------------------------------|---------------------------|

| Fusion Compiler: Jumpstart             | Fusion Compiler: Design<br>Creation & Synthesis | Fusion Compiler: Design<br>Implementation | Fusion Compiler: DFT<br>Synthesis | Fusion Compiler: UPF      |

| Introduction                           | Introduction & GUI                              | Floorplanning                             | Introduction                      | Introduction to UPF       |

| Design Setup and Reading<br>RTL Design | Reading RTL                                     | Setting up CTS                            | Scan Testing and Flows            | Power Domains             |

| NDMs/CLIBS                             | Objects, Attributes,<br>Application Options     | Running CTS (CCD+classic flow)            | Test Protocol                     | Power Strategies          |

| Floorplan and UPF data                 | Compile Flows and Setup                         | Routing                                   | DFT Design Rule Checks            | Supply Network            |

| Compile Flow                           | NDM Cell Libraries                              | Routing DRC                               | DFT DRC GUI Debug                 | Power States              |

| Timing Setup and CCD                   | Loading UPF and Floorplan                       | Via Ladder                                | DRC Fixing                        | Fusion Compiler and UPF   |

| Power Optimization                     | Timing Setup & OCV                              | Post-route Optimization                   | Top-Down Scan Insertion           | Fusion Compiler Reporting |

| Top Level Synthesis                    | CCD Optimization                                | Signoff                                   | Advanced Scan Insertion           |                           |

| Design Implementation                  | Power Optimization                              |                                           | Bottom-up Scan Insertion          |                           |

|                                        | Additional Compile Settings and Techniques      |                                           | Export                            |                           |

|                                        | Hierarchical Synthesis                          |                                           | On-Chip Clocking (OCC)            |                           |

|                                        |                                                 |                                           | DFTMAX                            |                           |

|                                        |                                                 |                                           | Advanced Topics                   |                           |

| 👰 🚛 🕹 💿 🔞 🔘                            | 👰 🔛 🕁 💿 🏐                                       | 🚇 艇 🕁 💿 (2) 🔘                             | 👰 🛴 🕹 💿 📀 🔘                       | 🖳 🕹 💿 📀 🔘                 |

#### SYNOPSYS®

Badge

Legend

Self-paced Learning

Instructor-Led Training Downloadable Lab Cloud-based Lab (#) Duration in Days

### FC/ICC II Hierarchical Design Planning Learning Path

#### Course 1

Fusion Compiler: SOC Design Planning

Initial Design Planning

**IO Planning**

From Commit to Abstract Creation

VA and Block Shaping

Macro Placement

PG PPNS

Pin Placement

Timing and Budgeting

Integration/Assembly

#### Fusion Platform Methodology Learning Path

#### Course 1

Fusion Platform Methodology: Jumpstart

Introduction & Overview

**Organization & Structure**

Lab Example

Installation & Setup

FCRM for FPM Users

FAQ – Common Topics

#### HAPS® Hardware Learning Path

| Course 1                               | Course 2                                |

|----------------------------------------|-----------------------------------------|

| HAPS-80: Hardware and<br>ProtoCompiler | HAPS-100: Hardware and<br>ProtoCompiler |

|                                        |                                         |

| Hardware Overview                      | Hardware Overview                       |

| System Clocks                          | System Clocks                           |

| HapsTrak3 Connectors                   | HapsTrak3 Connectors                    |

| Daughter Board and Cables              | UMRBus 3.0 Overview                     |

| Rack Mounting Solution                 | Daughter Boards and Cables              |

| Confpro                                | HAPS ProtoCompiler Flow                 |

| HAPS ProtoCompiler Flow                | Database Concepts                       |

| Database Concepts                      | HAPS ProtoCompiler Flow<br>Overview     |

| HAPS ProtoCompiler Flow<br>Overview    | Graphical User Interface                |

| Graphical User Interface               | Introduction to Debug                   |

| Introduction to Debug                  |                                         |

### IC Compiler II Learning Path

| Course 1                  | Cour                                        | se 2        |

|---------------------------|---------------------------------------------|-------------|

| IC Compiler II: Jumpstart | IC Compiler II: Block Level Implementation  |             |

| Introduction              | GUI Usage (lab)                             | Signoff     |

| Design/Timing Setup       | Objects, Attributes,<br>Application Options |             |

| NDMs/CLIBS                | Floorplanning                               |             |

| Floorplan                 | Placement                                   |             |

| Placement & Optimization  | NDM Cell Libraries                          |             |

| Clock Tree Synthesis      | Design Setup                                |             |

| Routing                   | Timing Setup                                |             |

| Top Level Synthesis       | Setting up CTS                              |             |

| Design Implementation     | Running CTS (CCD+classic flow)              |             |

|                           | Routing                                     |             |

|                           | Routing DRC                                 |             |

|                           | Via Ladder                                  |             |

|                           | Post-route Optimization                     |             |

| 👰 🔂 🕹 🙆 🔞                 | Top Level Implementation                    | 👰 🚰 🕁 💿 3 🔘 |

SYNOPSYS®

#### IC Validator Learning Path

| Course 1>                                 | Course 2                                  |                                         | Course 3                                         |

|-------------------------------------------|-------------------------------------------|-----------------------------------------|--------------------------------------------------|

| IC Validator: User<br>(DRC & LVS)         | IC Validator: Runset                      |                                         | IC Validatro: DRC Runset                         |

| Setup ICV and run DRC/LVS testcase        | Overview                                  | Compare                                 | Writing a basic "single file"<br>runset          |

| DRC Error Classification                  | Language introduction                     | Benefits of new language                | Writing debug output to<br>OASIS/GDS Using Layer |

| Execute DRC testcase with select commands | Command API                               | PXL compare syntax strategy             | Debugger<br>Understanding Error                  |

| LVL                                       | Writing a simple "flat" rule<br>runset    | Anatomy of compare functions            | Messages & Using<br>Diagnostic Functions         |

| Edtext options                            | Running a simple IC Validator runset      | Complementary compare functions         | Options Functions                                |

| Generate ICV formatted netlist            | Advanced programming concepts             | User-defined functions                  |                                                  |

| Generate equivalence options              | IC Validator API header files             | StarRC transistor-level extraction flow |                                                  |

| Debug LVS errors                          | Runset coding practices                   |                                         |                                                  |

| Using Short finder                        | Layout device extraction                  |                                         |                                                  |

| Using VUE & ICVWB with ICV                | Benefits of new language                  |                                         |                                                  |

|                                           | Runset structure                          |                                         |                                                  |

|                                           | Anatomy of device extraction<br>functions |                                         |                                                  |

|                                           | Property calculation                      |                                         |                                                  |

| 🚇 🚰 🕁 🙆 2 🔘                               | User-defined property<br>functions        | 🚇 🚰 🕁 🙆 🕄 🔘                             | 👰 🛴 🕹 💿 (1) 🤅                                    |

|                                           |                                           |                                         |                                                  |

Synopsys Confidential Information

### Library Compiler Learning Path

Course 1

### Language Learning Path

| Course 1                                   | Course 2                                  | Co                                                                           | ourse 3                              | Course 4                                        |

|--------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------|

| Language: SVA Formal<br>Verification       | Language: System Verilog<br>Assertion     | Language: System                                                             | Verilog for RTL Design               | Language: System Verilog<br>Testbench           |

| Introduction to SVA                        | Introduction                              | Basic System Verilog<br>Features                                             | Achieving High QoR Through<br>Coding | The Device Under Test                           |

| Formal Testbench                           | Types of Assertions                       | Implementing User Logic<br>Intent (combinatorial logic &                     |                                      | System Verilog Verification<br>Environment      |

| Coding Recommendation –<br>Do's and Don'ts | Action Blocks                             | latch)                                                                       |                                      | System Verilog Testbench<br>Language Basics - 1 |

| Resources                                  | Disabling/Combining/Embedd ing Assertions | Implementing User Logic<br>Intent (meaning of full and<br>parallel)          |                                      | System Verilog Testbench<br>Language Basics - 2 |

|                                            | Controlling Assertions                    | Implementing User Logic                                                      |                                      | Managing Concurrency in<br>System Verilog       |

|                                            | Sequences and Sequence<br>Repetition      | Intent (implementing registers)                                              |                                      | Object-Oriented<br>Programming: Encapsulation   |

|                                            | Sequences Operators                       | Implementing User Logic<br>Intent (implementing state                        |                                      | Object-Oriented<br>Programming: Randomization   |

|                                            | Synthesis Assertion<br>Coverage           | machines)                                                                    |                                      | Voltage Dependent Rule<br>Check                 |

|                                            | Assertion Libraries                       | Intent (wildcard and tri-state logic)                                        |                                      | Object-Oriented<br>Programming: Inheritance     |

|                                            |                                           | Advanced System Verilog<br>Features (packed or<br>unpacked array and struct) |                                      | Inter-Thread Communications                     |

|                                            |                                           | Advanced System Verilog                                                      |                                      | Functional Coverage                             |

|                                            |                                           | Features (System Verilog interface)                                          |                                      | System Verilog UVM preview                      |

| 👰 🚘 🕹 💿 🛈 🎯                                | 👰 🔛 🕁 💿 🕦 🔘                               | Advanced System Verilog<br>Features (System Verilog<br>package)              | 👰 🔂 🕁 💿 🕦 🔘                          | 🚇 🚰 🕂 💿 3 🛇                                     |

#### Legend

**Synopsys**°

#### Language Learning Path

Course 5

Language: System Verilog Verification using UVM

System Verilog OOP Inheritance Review

UVM Structural Overview

Modeling Stimulus (UVM Transactions)

**Creating Stimulus Sequences** (UVM Sequence)

Component Configuration and Factory

TLM Communications

Scoreboard & Coverage

**UVM Callback**

Advance Sequence/Sequencer

Phasing and Objections

Register Layer Abstraction (RAL)

Summary

Legend

### LynxNXT Learning Path

Course 1

LynxNXT: Foundation

Introduction

Variable Editor

Flow Editor

**Execution Monitor**

Failure Debug

Exploration

Command Line Interface

Working with FPM

ПÌ

#### PrimeLib Learning Path

Course 1

PrimeLib: Foundation

**Tool Introduction**

Global Setting to start characterization

Cell Level Setting to Configure Arcs

Different Characterization flow

Creating multiple Connect Database

Debugging and Troubleshooting

Complex Cell Characterization

Timing Characterization

Constraint Timing Characterization

**Power Characterization**

Legend

### PrimePower Learning Path

| Course 1 |                                      | Course 2                              |                                    |  |

|----------|--------------------------------------|---------------------------------------|------------------------------------|--|

|          | PrimePower: Jumpstart                | PrimePower: Foundation                |                                    |  |

| F        | Power Analysis Input                 | Introduction                          | PrimePower – Session Based<br>Flow |  |

| F        | Power Components                     | Power Analysis                        | Check & Report Power               |  |

| L        | eakage Power                         | Power Components                      | Report Switching Activity          |  |

| h        | nternal Power                        | Leakage Power                         | Summary                            |  |

| S        | Switching Power                      | Internal Power                        |                                    |  |

|          | nputs & Outputs of Power<br>Analysis | Switching Power                       |                                    |  |

|          | Simulation Activity Files            | Leakage & Internal Power<br>Data      |                                    |  |

| F        | Flow & Report                        | Input & Outputs of Power<br>Analysis  |                                    |  |

|          |                                      | PrimePower Analysis Modes             |                                    |  |

|          |                                      | Simulation Activity Files             |                                    |  |

|          |                                      | RTL Activity Flow                     |                                    |  |

|          |                                      | Gate-Level Activity Flow              |                                    |  |

|          |                                      | PrimePower Analysis<br>Accuracy       |                                    |  |

|          |                                      | PrimePower Standalone –<br>ASCII Flow |                                    |  |

| _        |                                      |                                       |                                    |  |

Synopsys®

### PrimeSim Learning Path

| Course 1                                          | Course 2                                | Course 3                                                  | Course 4               |

|---------------------------------------------------|-----------------------------------------|-----------------------------------------------------------|------------------------|

| PrimeSim: Jumpstart                               | PrimeSim: Foundation                    | PrimeSim: Advance                                         | PrimeSim: Advance      |

| PrimeSim Static CCK<br>Introduction               | PrimeSim XA Introduction                | CCK Advanced ERC and<br>ESD Checks                        | Interactive Mode       |

| PrimeSim CCK Built-In<br>Checks                   | PrimeSim XA Netlist format<br>Support   | CCK Propagation Engine –<br>XPL and Analog Propagation    | Distributed Processing |

| PrimeSim CCK Interactive<br>Debugging Commands    | PrimeSim XA Analyses support            | CCK Custom Programmable<br>Checks                         | Monte-Carlo (MC)       |

| PrimeSim CCK False Error<br>Pruning               | Command/Option Usage & Precedence Rules | Custom Check Assertion                                    | MOSRA                  |

| Custom Compiler – PrimeSim<br>CCK : Setup and run | PrimeSim XA Post-Layout<br>Simulation   | GUI : Cross-Probe, Filtering,<br>Waiver, Grouping, export | Aging and Self-Heating |

|                                                   | PrimeSim XA Command Line<br>Usage       |                                                           |                        |

|                                                   | PrimeSim XA Log File Details            |                                                           |                        |

|                                                   | Accuracy and Speed Trade-<br>off        |                                                           |                        |

|                                                   | Back-Annotation & XBA                   |                                                           |                        |

|                                                   | Probing in PrimeSim XA                  |                                                           |                        |

|                                                   | PrimeSim XA .ALTER Usage                |                                                           |                        |

|                                                   | PrimeSim XA .DATA Usage                 |                                                           |                        |

|                                                   |                                         |                                                           |                        |

| 👰 🛴 上 🙆 fi2 🔘                                     | 👰 🚰 🛃 🙆 2 🔘                             |                                                           | 👰 🚰 🕹 🙆 🕦 🔘            |

Synopsys Confidential Information

#### PrimeTime Learning Path

| Course 1                         | Course 2                                      | Course 3                              | Course 4                           |  |

|----------------------------------|-----------------------------------------------|---------------------------------------|------------------------------------|--|

| PrimeTime: Jumpstart             | PrimeTime: Foundation                         | PrimeTime: HyperScale                 | PrimeTime: Scalable STA            |  |

| Overview                         | Introduction to STA in<br>PrimeTime           | Introduction HyperScale               | Hierarchical Methodologies         |  |

| PrimeTime Implementation<br>Flow | STA Concepts and Flow in<br>PrimeTime         | Flat Context Flow                     | HyperScale                         |  |

| PrimeTime Inputs & Outputs       | Methodology: Qualifying<br>Constraints        | Bottom Up Flow                        | HyperScale Hybrid Flow             |  |

| Timing Analysis Flow             | Methodology: Generating<br>Reports            | Generating HyperScale Block<br>Models | Distributed & Scenario<br>Analysis |  |

| Load Design & Check              | Constraining Multiple Clocks                  | Constraint Consistency                | HyperGrid                          |  |

| Load Library & Check             | Additional Checks and<br>Constraints          | Clock Mapping                         | DMSA                               |  |

| Read Parasitic & Check           | Correlation: POCV and AWP<br>Analysis         | HyperScale Top-Down Flow              | DVFA/SMVA                          |  |

| Source Constraints & Check       | Signoff: Path Based Analysis (PBA)            | HyperScale-Driven ECO                 | PBA Technologies                   |  |

| Constraints Completeness         | Signal Integrity: Crosstalk<br>Delay Analysis | Summary                               | Best Practices                     |  |

| Coverage Analysis                | Signal Integrity: Crosstalk<br>Noise Analysis |                                       |                                    |  |

| Report                           | Timing Closure: ECO/What If<br>Analysis       |                                       |                                    |  |

| Saving & Exit                    | Large Data: DMSA and<br>Hyperscale Analysis   |                                       |                                    |  |

|                                  |                                               |                                       |                                    |  |

| 🚇 🔬 🕹 💿 112 🔘                    |                                               |                                       |                                    |  |

Synopsys Confidential Information

####

### Recommend Learning Journey: Physical Designer

| Course 1                               | Course 2>                                       | Course 3                                  | Course 4                          | Course 5                                |

|----------------------------------------|-------------------------------------------------|-------------------------------------------|-----------------------------------|-----------------------------------------|

| Fusion Compiler: Jumpstart             | Fusion Compiler: Design<br>Creation & Synthesis | Fusion Compiler: Design<br>Implementation | Fusion Compiler: DFT<br>Synthesis | Fusion Compiler: SOC<br>Design Planning |

| Introduction                           | Introduction & GUI                              | Floorplanning                             | Introduction                      | Initial Design Planning                 |

| Design Setup and Reading<br>RTL Design | Reading RTL                                     | Setting up CTS                            | Scan Testing and Flows            | IO Planning                             |

| NDMs/CLIBS                             | Objects, Attributes,<br>Application Options     | Running CTS (CCD+classic flow)            | Test Protocol                     | From Commit to Abstract<br>Creation     |

| Floorplan and UPF data                 | Compile Flows and Setup                         | Routing                                   | DFT Design Rule Checks            | VA and Block Shaping                    |

| Compile Flow                           | NDM Cell Libraries                              | Routing DRC                               | DFT DRC GUI Debug                 | Macro Placement                         |

| Timing Setup and CCD                   | Loading UPF and Floorplan                       | Via Ladder                                | DRC Fixing                        | PG PPNS                                 |

| Power Optimization                     | Timing Setup & OCV                              | Post-route Optimization                   | Top-Down Scan Insertion           | Pin Placement                           |

| Top Level Synthesis                    | CCD Optimization                                | Signoff                                   | Advanced Scan Insertion           | Timing and Budgeting                    |

| Design Implementation                  | Power Optimization                              |                                           | Bottom-up Scan Insertion          | Integration/Assembly                    |

|                                        | Additional Compile Settings and Techniques      |                                           | Export                            |                                         |

|                                        | Hierarchical Synthesis                          |                                           | On-Chip Clocking (OCC)            |                                         |

|                                        |                                                 |                                           | DFTMAX                            |                                         |

|                                        |                                                 |                                           | Advanced Topics                   |                                         |

| 👰 🚛 🕹 💿 🕡                              | 👰 🏭 🕁 💿 🏐                                       | 👰 🔛 🕁 💿 2 🎯                               | 🚇 🔛 🕁 💿 (2) 🎯                     | 👰 🔛 🕁 💿 🔇                               |

#### Recommend Learning Journey: Physical Designer

| Course 6                            | Course 7                            |

|-------------------------------------|-------------------------------------|

| Fusion Compiler: UPF<br>Fundamental | Reference Methodology:<br>Jumpstart |

|                                     |                                     |

| Introduction UPF                    | Introduction & Overview             |

| Power Domains                       | Organization & Structure            |

| Power Strategies                    | Running RM                          |

| Supply Network                      | Demo                                |

| Power States                        |                                     |

| Fusion Compiler and UPF             |                                     |

|                                     |                                     |

|                                     |                                     |

|                                     |                                     |

**Synopsys**°

#### Reference Methodology Learning Path

#### Course 1

Reference Methodology: Jumpstart

Introduction & Overview

**Organization & Structure**

Running RM

Demo

### RTL Architect Learning Path

| Course 1>                     | Course 2                                       |

|-------------------------------|------------------------------------------------|

| RTL Architect: Jumpstart      | RTL Architect: Using RTL<br>Restructuring      |

|                               |                                                |

| Introduction & Overview       | RTL Restructuring                              |

| RTL Architect Key Features    | Group                                          |

| Predictive Engine             | Ungroup                                        |

| Unified GUI                   | Reparent                                       |

| Physical Floorplaning         | Restructured RTL, SDC,<br>UPF, SAIF Generation |

| Power Analysis                | Reparenting and Writing RTL                    |

| Logic Restructuring           | Demo                                           |

| Constraint Management         |                                                |

| Flows                         |                                                |

| rtl_opt Mega Command          |                                                |

| Block-Level Flow/Breakpoints  |                                                |

| Hierarchical Flow/Breakpoints |                                                |

|                               |                                                |

|                               |                                                |

Legend Self-paced Learning Instructor-Led Training ,√, Downloadable Lab (0) Cloud-based Lab # Duration in Days  $\bigcirc$ Badge

П

**Synopsys**°

© 2023 Synopsys, Inc. 32

#### StarRC Learning Path

| Course 1                       | Course 2                    |  |

|--------------------------------|-----------------------------|--|

| StarRC: Jumpstart              | StarRC: Foundation          |  |

|                                |                             |  |

| Interconnect                   | Extraction Fundamentals     |  |

| Coupling Capacitance           | Gate level Extraction       |  |

| Classes of Extractors          | Transistor Level Extraction |  |

| Input for Parasitic Extraction | Selective Netlist           |  |

| StarRC Flow                    | Field Solver                |  |

| SMC Flow                       | Process Modelling           |  |

| ITF File                       | Metal Fills                 |  |

|                                |                             |  |

Legend

#### Synopsys®

|        | Bad       | ge   |

|--------|-----------|------|

| © 2023 | Synopsys, | Inc. |

#### SaberRD Learning Path

Course 1

SanerRD: Foundation Training Series

| Timing Domain Analysis                                |          |       |  |   |

|-------------------------------------------------------|----------|-------|--|---|

| Schematic Capture & Parts<br>Library                  |          |       |  |   |

| Operating Points & Small<br>Signal Frequency Analysis |          |       |  |   |

| Test Automation                                       |          |       |  |   |

| Design Optimization                                   |          |       |  |   |

| Introduction to Modeling                              |          |       |  |   |

| Import SPICE Models                                   |          |       |  |   |

| Modeling with Table Look-Up                           |          |       |  |   |

| Modeling with StateAMS                                |          |       |  |   |

| Robust Design & Sensitivity<br>Analysis               |          |       |  |   |

| Monte Carlo & Pareto                                  |          |       |  |   |

| Worst-Case Analysis                                   |          |       |  |   |

| Fault Analysis                                        |          |       |  |   |

| Stress Analysis                                       | <u>B</u> | ^<br> |  | 3 |

|                                                       |          |       |  |   |

Legend

ПÌ

## Synplify: Learning Path

Course 1

#### Synplify: Foundation

Introduction to Synplify Elite Flow

Creating and Running Synplify Project

View Log File

HDL Analyst

Handling High Reliability Designs

Implementing Fault Tolerant FSMs

ECC RAM Inferring

Importing Quartus IP in Synplify Projects

Debugging with SpyGlass

Debugging with VCS

Identify Instrumentor and Debugger

п

#### TestMAX Advisor Learning Path

#### Course 1

TestMAX: Jumpstart

Early Testability Goals and Reports

Debug using the GUI

**Transition Delay Checks**

Random Resistant Fault Analysis and Test Points

Post stitch DRC Checks

**Connectivity Checks**

Flow With TestMAX Manager

### TestMAX Access Learning Path

| Course 1>                                                 | Course 2                            |

|-----------------------------------------------------------|-------------------------------------|

| TestMAX: Jumpstart                                        | TestMAX: ATPG                       |

|                                                           | Monufacturing Test and              |

| TestMAX Access structure                                  | Manufacturing Test and<br>ATPG      |

| IEEE 1687 interface to drive internal instruments through | Building ATPG Models                |

| TDR                                                       | Running DRC                         |

| SIBs                                                      | Fault Models and Managing Faults    |

| Define Ring configuration                                 | Controlling ATPG                    |

| Definition of Server and Subserver                        | Post ATPG Analysis                  |

| AIT                                                       | Pattern Validation                  |

| PDL Pattern Porting                                       | At-Speed Testing and<br>Constraints |

| PDL data packetization                                    | Transition Delay Testing            |

| Validation of AIT                                         | On-Chip Clocking and<br>Compression |

|                                                           | Path Delay Testing                  |

|                                                           | Power Aware ATPT                    |

|                                                           | Conclusion                          |

|                                                           |                                     |

**Synopsys**°

#### TestMAX FuSa Learning Path

#### Course 1

TestMAX FuSa: Jumpstart

Functional Safety for Automotive Designs

TestMAX FuSa: Introduction

TestMAX FuSa: Static FuSa Analysis

Running TestMAX FuSa: Requirement & Constraints

Functional Safety reporting in TestMAX FuSa

п

####

#### TestMAX Manager Learning Path

#### Course 1

TestMAX Manager: Jumpstart

Launching and Configuring tool

Objects, Attributes, Application Options

NDM Cell Libraries

**Timing Setup**

#### TestMAX SMS Learning Path

Course 1

TestMAX-SMS: Architecture

Introduction

SMS Wrapper

SMS Processor

MMB Processor

SMS Server

Conclusion

пÌ

#### TestMAX XLBIST Learning Path

Course 1

TestMAX XI BIST: lumostart

| I ESTIMAX XLB                                                  | IST: Jumpstart                     |

|----------------------------------------------------------------|------------------------------------|

|                                                                |                                    |

| LogicBIST basics                                               | Troubleshooting and Debug<br>hints |

| XLBIST architecture                                            | Intro to AIT                       |

| XLBIST and SEQ modes of operation                              |                                    |

| IEEE 1500 I/F and internal resources                           |                                    |

| XLBIST patterns and interval definition                        |                                    |

| Random Resistant Fault<br>analysis and Test Point<br>insertion |                                    |

| X propagation analysis and fixing                              |                                    |

| OCC and Clock Weights                                          |                                    |

| Reset Controller and Reset<br>Weights                          |                                    |

| Programmable SE Timing<br>Margin                               |                                    |

| Remap XLBIST Patterns for<br>Debug and Diagnosis               |                                    |

| Validation of XLBIST patterns                                  |                                    |

| Porting of XLBIST patterns                                     |                                    |

| Simulation steps for validation                                | 🚇 🚛 🕹 🙆 2 🍥                        |

SYNOPSYS®

#### **Tweaker Learning Path**

Course 1

Tweaker: ECO

ECO Flow and Interoperability

Basic ECO Flow

Timing ECO

Useful Skew Clock ECO

Power ECO

Area Recovery

Reliability Recovery

Advanced ECO Features

Hierarchy Design Flow

П

**Synopsys**°

#### VC Formal Learning Path

Course 1

VC Formal: Foundation

Introduction

Formal Verification Methodology

SVA for Formal Verification

VC Formal Basic

VC Formal Navigator

Legend Self-paced Learning Instructor-Led Training **,**↓, Downloadable Lab  $\langle \mathbf{O} \rangle$ Cloud-based Lab (# Duration in Days {(~) Badge

П

### Zebu Learning Path

| Course 1>                                            | Course 2                                  |

|------------------------------------------------------|-------------------------------------------|

| Zebu: Foundation                                     | Zebu: Advanced                            |

| Introduction to Emulation                            | Transactors – Guide to integration + List |

| ZeBu overview (HW and SW)                            | Low Power emulation                       |

| ZeBu Ecosystem                                       | Virtual Host and Devices                  |

| ZeBu Compile                                         | ZeBu Debug                                |

| ZeBu Runtime                                         | Hybrid Emulation                          |

| Tuning ZeBu for High<br>Performance / TAT / Capacity | ZeBu Empower – SW based power analysis    |

| Gate Level emulation                                 | Real world interfaces with speed adaptors |

|                                                      |                                           |

П