# Synopsys Insight

DESIGNING A SMARTER FUTURE FROM SILICON TO SOFTWARE

Issue 2 | 2016

Subscribe

## **EDA Tools**

Verify Software Bring-Up on Your IC Design Before Sending It to the Fab

How to Create a Testbench With Synopsys Verification IP and UVM in 5 Steps

Addressing Physical Design Challenges in the Age of FinFET and Smarter Design

Multi-Level Physical Hierarchy Floorplanning vs. Two-Level Floorplanning

## Semiconductor IP

IP for the Era of FinFET and **Smart Designs**

From Silicon to Software: A Quick Guide to Securing IoT **Edge Devices**

## **Customer Spotlight**

Movidius Keynotes IC Compiler II Technology Symposium With Vision of Smart, Connected Machines and Networks

## **Software Integrity**

Software Is Everywhere — And So Are the Vulnerabilities

Agile Development for **Application Security Managers**

## **Additional Resources**

**Events**

**Seminars**

**Webinars**

Synopsys Users Group (SNUG)

#### **Customer Spotlight**

## Movidius Keynotes IC Compiler II Technology Symposium With Vision of Smart, Connected Machines and Networks

Mike Santarini, Director of Corporate Communications Strategy, Synopsys

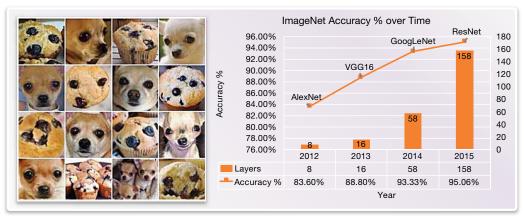

"Is it a Chihuahua's face or a blueberry muffin?" That is one of many problems that can be solved when deep neural networks are implemented close to the image sensors at the network's edge, where SoCs with smart vision sensing can perform low-power image classification—a system envisioned by the high-tech industry now striving to bring higher intelligence to everything connected.

In the keynote at the Synopsys IC Compiler II Technology Symposium (where Intel, Samsung, Broadcom, Mellanox and ecosystem partners ARM and TSMC also presented), Movidius' vice president of marketing, Gary Brown, captivated the audience of 250 IC design experts by laying out Movidius' vision of how a mix of innovative architectural design and advanced IC design tools (such as Synopsys' IC Compiler II™) is enabling companies like Movidius to implement SoCs with greater algorithmic intelligence, advanced vision sensing, and deep learning techniques. These devices bring localized processing and intelligence to the growing number of products connected to (aka at the edge of) the network, thereby offloading an increasing amount of processing from the massive, power-hungry cloud datacenters. This smart processing at the edge in turn enables systems companies to quickly bring to market autonomous cars and drones, augmented reality and virtual reality (AR/VR) products, as well as advanced security systems with intelligent analytics. And it helps companies improve the accuracy, power efficiency, and operating expenditure (OPEX) of deep neural networks (Figure 1).

Having recently announced that it is to be acquired by Intel, Movidius (San Mateo, CA) is a 10-year-old developer of visually-intelligent SoCs. The company's mission is to give the power of sight to machines in this emerging era of smart, connected everything. Movidius' flagship Myriad 2 vision processing unit (VPU) is featured in DJI's Phantom 4 autonomous drone, was selected by Google for machine learning and by FLIR for smart cameras, and is in Lenovo's virtual reality products. It will soon offer a version of its chip on a USB stick, called Fathom, that researchers/developers can plug into USB-supported devices to offload machine learning and execute convolutional neural networks to solve problems in image classification.

DJI's Phantom 4 autonomous drone shows off the advanced processing features of Movidius' Myriad 2. "The Phantom 4 is remarkable," said Brown. "It can take selfies of people in motion (running, biking, or skiing) while navigating around obstacles. Evidently this is a very big and required application today." Users can run the drone in multiple modes, including navigating via GPS and manually. "It is able to detect and move around very well using depth cameras," said Brown. "You can actually attempt to fly it directly into a wall and it will avoid collision on its own. These are pretty advanced intelligent functions for a drone."

While machine intelligence and artificial intelligence algorithms to detect objects and identify people have been around for more than 30 years, design teams previously had to implement those algorithms on large computers. "With all of our pioneering efforts in integrated circuits, we are now able to bring this level of intelligence to devices that are very small, sometimes battery operated, working at the network edge, right next to some image sensors," explained Brown. "It allows companies to create autonomous drones that have to detect things, track things, and classify things."

The technology allows companies to add intelligence to many other applications, such AR/ VR systems. "Augmented reality and virtual reality bring together some of the most difficult applications all into one very compact space," said Brown. "You are wearing a virtual reality product on your head, so it has to detect your gestures and detect your movement and know where your head is positioned precisely to understand where to position things in your field of view."

Brown points out that eye/gaze tracking in a VR headset is quite complex. "The eye/gaze tracking algorithm is important because it relaxes the workload of the GPU in a system, allowing the GPU to render and display high resolution only where the eye is pointed," Brown said. "As your eyes are moving, if the display only renders high resolution where you are looking, then it will seem to the user that the whole screen appears to be high resolution. This means you can lower the GPU's workload and save on power."

But he added that eye/gaze tracking is just one of the handful of complex applications required to run simultaneously in a VR system. VR brings together a lot of different sophisticated technologies such as depth, tracking, simultaneous localization and mapping (SLAM), gesture recognition, and classification. "All these applications have to be running in parallel, which is why you see a lot of these system tethered to large, high-performance PCs with very high-end GPUs," said Brown. "Untethering and implementing these applications in a low-power SoC is a tough architectural and design challenge."

The field of deep learning presents additional challenges and opportunities for smart vision processing SoCs. "Deep learning is a hot topic," said Brown. "There is a huge need to be able to solve problems that engineers don't know how to write an algorithm to solve." Brown said, for example, that most people can tell whether a friend is giving them a fake smile or genuine one, but making that distinction isn't easy for a machine. "It's really difficult to write an algorithm to do that, but it is easy for a human being because you have close to 100 billion neurons in your head," said Brown. "How do you do the same thing in an integrated circuit? What people have done over the last decade is come up with models for these neurons. A neuron is, in a sense, taking a network of say 1,000 neighboring neurons and all those neurons are sending a positive or negative charge. You have to sum over time and sum over space that charge to determine what that output should be. That's how a real neuron works. But how do you create a model of that? How do you develop a circuit to be able to do the same thing?"

Brown said that the answer is to build a neural network. "We take, for example, a field of pixels. You can cause each pixel to activate and be summed with some weighting by a first level of neurons and then have the outputs go to another level of neurons for additional weighting," he explained. "You detect in an image, for example, small features with the initial layer of neurons, then move to another layer of neurons and detect bigger and bigger features to ultimately decide: is this field of pixels an A, B, C, D, or E that I'm looking at?"

With a deep neural network approach and extensive testing/training of a network, networks can identify objects and the identities of people in pictures or video, translate languages, and classify audio and can also be applied to many other types of image or vision processing, said Brown.

One of these tests asks the deep neural networks to distinguish between pictures of blueberry muffins and pictures of the faces of tan Chihuahuas (Figure 1). "'Is it a Chihuahua or a muffin?' -is a difficult problem to solve," said Brown. "It's difficult to write an algorithm that detects the difference. [The muffins and Chihuahuas] all seem to have cute eyes and a cute nose."

"Movidius aspires to create SoCs with the sophistication of the human brain."

"...today we are seeing an explosion in the use of neural networks because of the sophistication and capabilities in ICs we are designing."

Figure 1. The ability of deep neural networks to accurately distinguish between objects has improved dramatically over the last five years, but further gains in accuracy over the last two has required exponential increases in neural layers and network horsepower

Brown said that deep learning networks have become quite accurate in a relatively short amount of time, but in the last two years, companies have had to add exponentially more neural layers to their networks to achieve marginal gains in accuracy improvements. According to Brown, this is where Movidius SoCs can step in to do essentially localized processing in the many types of vision systems connected to the network.

"What's truly interesting about deep learning today is that the integrated circuits we are designing can now sustain enough performance to be able to run very complex neural networks in real time, where before you were only able to run very simple analog networks to do similar things," said Brown. "But today we are seeing an explosion in the use of neural networks because of the sophistication and capabilities in ICs we are designing."

Brown said that processing at the edge of the network can make a network 1 million times more energy efficient, consume 10,000 times less bandwidth, and have 1,000 times lower latency, while giving networks additional benefits such as improved privacy and fault-tolerance or continuity of service.

Brown said that Movidius aspires to "create SoCs with the sophistication of the human brain."

"If you think about it, doing 10 to the 17<sup>th</sup> power calculations per second is equal to 100,000 teraflops. If you could do it in a tiny chip, how fascinating would that be? And if you could do it in just 20 watts of the human brain, that's something like 500 gigaflops per watt. That's an amazing amount of performance. We strive to get closer to the performance of the human brain. It so happens that around 50% of the brain's cortex is dedicated to the vision sense," Brown explained.

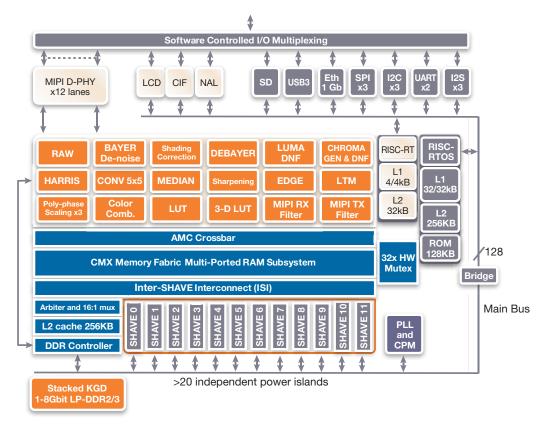

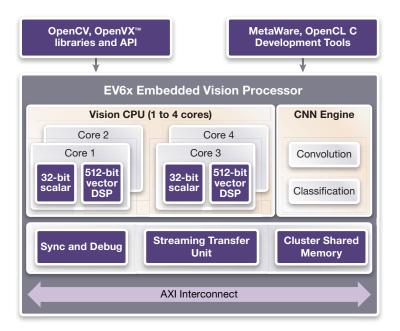

While not quite as sophisticated as the human brain, the architecture of Movidius' Myriad 2 vision processing unit is highly advanced. In a single device, it combines:

- Configurable imaging and vision hardware engines

- ▶ 12 programmable DSPs designed to crunch complex vison and imaging algorithms at very high performance but low power consumption

- ▶ Low-power, zero-latency, on-chip memory to support localized processing

- Two RISC CPUs to run the RTOS, firmware, and runtime scheduler

Image processing traditionally takes a camera input through an image sensor pipeline and feeds the image into a programmable processor that does computer vision. "What we did was break the problem into parts and then merge them all together in a more flexible way," said Brown. "We take the image sensor pipeline and implement it with a series of flexible blocks so that you can tap in and out at any part of the pipeline to run any kind of vision processing algorithms you choose. For us, image processing or vision sensing or machine intelligence is all the same thing."

The VPU includes an array of proprietary on-chip vector processing blocks, internal CPUs for scheduling, and a user-programmable CPU for further customization. The VPU also includes several types of interfaces from USB3 to UART to 12 lanes of high-speed MIPI (Figure 2).

Figure 2. Movidius' Myriad 2 MA2x50 employs an ingenious, sophisticated architecture

Brown said the design, which Movidius implemented on a 28-nm planar process, had more than 20 independent power islands. The company's design team used Synopsys IC Compiler II for physical design of the VPU.

"Synopsys has been a friend of Movidius chip after chip over the years," said Brown. "We have had a number of successful tapeouts together. "Specifically with IC Compiler II, what we have seen is that we can implement a design change in less than a day, where it previously took roughly a week. IC Compiler II gave our team a 10x improvement in turnaround time."

Brown said Movidius' designers also took advantage of the IC Compiler II platform's concurrent clock and data features to achieve faster timing closure while simultaneously lowering the power of clock trees.

The design allowed the company to pack its elaborate architecture into a 6mm x 6mm flipchip package. "Customers are pretty amazed to see that we packed all of this into a tiny flip chip," concluded Brown. "I would say our success in AR/VR, drones, and surveillance can be partly attributed to the fact that the PCB space required for the chip is minimal. We see a huge opportunity to make smaller yet highly performance-efficient SoCs for machine intelligence applications." ■

#### **About the Author**

Mike Santarini, Director of Communications Strategy for Synopsys Corporate Marketing, is a former content strategist at Xilinx and publisher of Xcell Journal and Xcell Software Journal. Prior to his 8 years at Xilinx, he covered the EDA and semiconductor industries for 14 years at trade publications EE Times, EDN and Integrated Systems Design.

#### **EDA Tools**

## Verify Software Bring-Up on Your IC Design Before Sending it to the Fab

Mike Santarini, Director of Corporate Communications Strategy, Synopsys

The world of IC design verification is becoming even more complex in the era of smart design. As if it wasn't hard enough to verify the functionality of hundreds of blocks, multiple types of on-chip processors and high-speed I/O, hundreds of voltage islands, and thousands of clocks on today's SoC designs, verification teams are finding it's becoming mandatory to verify that an OS will boot up on a design and even run applications before teams can send their design off to the foundry to be manufactured. And leading-edge design teams are already adding more sophisticated testing to this relatively new step of early software bring-up.

"SoC verification is changing dramatically," said Michael Sanie, vice president of marketing in the Synopsys verification group. "Verifying hardware in the context of software is dominating verification activity today." In the past, Sanie explained, verification teams would develop various types of stimuli, run simulation, and use other verification tools to find bugs in their design. They would fix the bugs and then send their design to the fab to make a chip. Once they had silicon back, the software team would bring up software on the silicon and adjust the software until the combined design functioned adequately.

Around 10 years ago that began to change. Companies in the mobile handset market began developing smart phones that required SoC platform ASSPs to support dramatically more software and required SoC design teams to complete their designs in tighter market windows. "They quickly discovered they could no longer wait until the chip came back from the fab to start looking at the software," said Sanie. If the chip came back from the fab and didn't have the functionality or performance to support the software they or their OEM customer planned to run on it, they needed to redesign and respin the chip, which meant they were late to market and took a big hit to profit margins. This, of course, likely means the end of the relationship with the OEM too. Performing software bring-up at this stage also, of course, enabled software developers to get an earlier jump on software development, speeding the handset vendor's overall time-to-market in an increasingly competitive smart handset market.

Sanie added that over the last 5 years, as smart technologies have grown into other application spaces such as embedded vision, automotive, datacenter, SDN/NFV, and IoT, early software bring-up on designs has become the rule rather than the exception. "I don't know of many verification teams today that will send their chip to tapeout without performing some amount of software bring-up on the design before they send the design to the fab — you can't afford not to do it," said Sanie.

Today, how much software design teams run before signing off on the silicon depends on the market they are targeting. Sanie said that because of the accelerating logistics and time-to-market pressure involved in most markets, most companies don't run their entire software stack on the design before sending the design out to be manufactured. "At the very least, they do check that they can boot up Android or Linux on the design before the design is sent to the fab," he said.

In the age of smarter technologies, in which more sophisticated hardware and growing stacks of software are combined to perform more complex tasks and a wider and greater number of simultaneous tasks, bringing up software and confirming it runs seamlessly with the targeted hardware seems to be evolving rapidly from a "nice to have" to a mandate in some industries.

The automotive industry's ISO 26262 standard for automotive design is a prime example. It recommends that automotive suppliers perform extensive IC-level HW/SW safety testing and recommends that teams document their testing methods and findings in detail (see Insight 1, 2016 automotive special issue). And in a growing number of industries (IoT, smart cities, smart

infrastructure, autonomous driving, etc.) that employ smarter, connected systems, security testing is becoming mandatory, not just safety testing. While the standards do not explicitly mandate pre-silicon HW/SW verification today, the increasing complexity of the devices and software running on them seem to indicate they will become mandated in the not-toodistant future.

Arturo Salz, a scientist in the Synopsys Verification Group, points out that in many smart systems, the close coupling of complex ICs and complex software stacks are becoming more important. Today's smart SoCs can have hundreds of voltage islands, thousands of clocks, multiple processors, and run in multiple modes. What's more, to serve more markets with one piece of silicon, semiconductor companies are increasingly creating heterogeneous processing platforms, essentially everything-including-the-kitchen-sink ASSP SoCs, that can run many different types of OSs and RTOS and software. A software glitch or a malicious program can cause a processor core to excessively overclock and burn itself up or quickly wear out a system's battery, so silicon has to have wider tolerances and be able to return to a safe and recoverable state if something in software goes haywire.

Sanie added that while software bring-up is becoming mainstream and even mandatory in some markets, it is still "early days" for what tasks design teams perform during this relatively new step of early software bring-up. "We are starting to see customers increasingly perform power profiling and power estimation during this phase," said Sanie. "Smart phone manufactures will emulate cell phone operations for days, running all different kinds of apps to identify power consumption characteristics and proactively identify potential issues. From these runs, they can get a better view of the power profile of their overall system and decide if they need to adjust the voltage islands on the chip design or make a system-level change like go to a bigger battery, etc." Salz added that software bring-up and power profiling require an exceptional level of hardware verification and software testing. "They can be tested independently but must also be tested together," said Salz.

But to bring up ever-more stacks of software on the designs of today's massive and massively complex IC, SoC, and heterogeneous platform ASSP designs requires an enormous amount of verification compute horsepower as well as a methodology adjustment to verify designs are functionally correct. "To bring up Android requires around 40+ billion or more cycles," explained Sanie. "That's why teams are moving to hardware for the early software bring-up." Sanie said it's also a big reason why emulation and FPGA-based prototyping are becoming mainstream and the market is growing.

Indeed, in their EDA earnings report for calendar Q2 2016, the big three companies in the EDA industry all cited growth in the emulation sector, indicating the need for hardware-assisted verification is growing. Sanie estimates that some of this growth can be attributed to design teams simply having more gates/transistors to work with (per Moore's Law) and a need for verification to handle these higher capacity designs. He predicts early software bring-up will be a new growth driver for the verification space, as the coupling of complex hardware and larger software stacks drive competition in the race for companies across most markets to bring smarter systems to market.

Sanie said that he believes Synopsys' ZeBu® is the fastest growing emulation family in the industry and asserts that ZeBu emulation is also the fastest in terms of raw performance, with design clocks running up to 5MHz. That's well above the 1 MHz performance design teams have traditionally been able to get out of emulation systems. Meanwhile, the HAPS® system can run a system clock in the range of 15MHz to 20MHz, typical. Sanie said that increasingly teams use the emulation systems for bring-up because, it gives teams a simulation-like environment to verify their designs. Design groups will use HAPS prototyping for developing software in the context of the entire system.

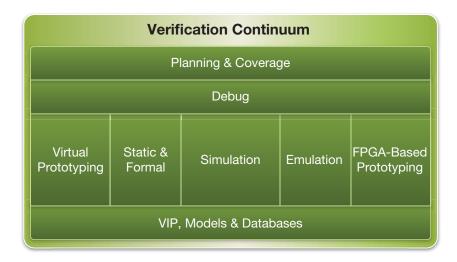

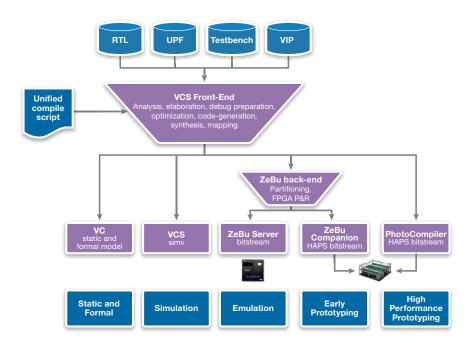

Sanie continued that the growth in Synopsys' emulation business is not based solely on the raw performance of ZeBu and HAPS systems but also on the completeness and seamlessness of Synopsys' integrated verification platform – the Verification Continuum™ (Figure 1).

"I don't know of many verification teams today that will send their chip to tapeout without performing some amount of software bring-up on the design before they send the design to the fab—you can't afford not to do it."

"Sanie said that he believes Synopsys' ZeBu is the fastest growing emulation family in the industry and asserts that ZeBu is also the fastest in terms of raw performance, with design clocks running up to 5MHz."

Figure 1. Synopsys' Verification Continuum platform offers new levels of integration and time-to-market savings.

"The Verification Continuum comprises best-in-class point tools at every step in the verification flow," said Sanie. "Best-in-class point tools throughout the verification portfolio is in and of itself compelling, but over the years, we've done a lot of work to integrate the tools into a seamless platform so that the verification tools across the platform not only have the fastest engines, but also share several native integrations including unified compile and unified debug capabilities. We architected these native integrations to significantly reduce the time it takes design teams to move a design from simulation to emulation to FPGA prototyping and to tackle debug challenges throughout the flow."

Sanie explained that with the unified compile capability, verification engineers can take, for example, the same RTL design block they implement in the VCS® simulator and move that block over to the ZeBu emulation system or to the HAPS FPGA-based prototyping system, and the design will maintain the same functional integrity across all three verification models (but, of course, run the functions faster in hardware emulation and prototyping). "With the unified compile capability, whatever you have in the simulation — whether it be RTL file, your UPF file, or whatever you have — you can use that same exact design in emulation and FPGA prototyping, no longer needing to modify the design itself to be able to bring it up in emulation or FPGA prototyping," added Sanie. Salz further added that simulation solutions typically work sequentially and are event driven (per the Verilog semantics), while hardware is highly parallelized. Unified compile includes the engines that allow the simulation, emulation, and FPGA prototyping to work congruently (Figure 2).

What's more, Sanie said that unified debug with Verdi® debug (the industry's de facto solution) means that verification teams can perform IC debug with same quality and integrity in whichever verification platform they choose. ■

Figure 2. The Verification Continuum platform's unified compile capabilities allows verification teams to move designs from simulation, emulation to FPGA prototyping with ease.

Tom Borgstrom, senior director of emulation product marketing at Synopsys, is quick to point out that no two customers do verification the exact same way and in many cases no two verification teams within the same company perform verification the same way. "The Verification Continuum platform doesn't dictate how teams must run verification," Borgstrom said. "It gives verification teams a lot of options to run whatever methodology they employ, but will also help them run their methodology more effectively with the highest quality tools and reliable flow between those tools."

For example, some companies may have multiple, very large designs and very large verification teams. They may start projects by having verification team members looking over the shoulders of designers and performing block-level simulation with VCS and Verdi tools immediately after designers complete each minor block. They may have a team of associates whose job it is to connect those blocks/builds into larger blocks and then run the larger blocks through simulation and emulation and Verdi debug, repeating the build and verification process until they have a complete chip design. They then run the entire chip design on an emulation system and debug the design for hardware bugs. Once they have the hardware verified and stable, they then have the software team bring up the required software before signing off on the chip design. Once the software team confirms the software bring-up works to their satisfaction, the design team sends the chip to the fab and the software team continues to the emulation system or FPGA prototype to develop and bring up more layers of software at a chip and full system level. "Some companies even use emulation systems to help diagnose post-silicon failures," said Borgstrom.

Other teams may want to perform software bring-up even faster and employ early software bring-up methodologies, in which verification teams typically run functional or behavioral models of known-good reused blocks in simulation and run new RTL blocks they've built for their new chip design in emulation. In doing so, they can typically speed up the overall clock cycle performance of the design to enable software teams to more quickly check if the chip design will be able to boot up their targeted OS or even bring up application software the design must run.

While silicon is being manufactured, they can also create a C-level model/virtual prototype of their design to allow both in-house software developers and end-customers get an early jump on application software development.

## How to Create a Testbench with Synopsys Verification IP and UVM in 5 steps

Amit Sharma, Director, Corporate Applications

Verification is one of the biggest challenges for IC designs and traditional methods have run out of steam. Writing individual tests is impractical for today's large, complex designs because the state space and number of test conditions are simply too large for verification engineers to code by hand, leading to insufficient test coverage. Limited project resources and time-to-market pressure is compounding the problem. The repercussions are clear — first-pass silicon success is harder to achieve.

To address these challenges, IC verification teams are turning to advanced and unified verification methodologies that leverage multiple technologies. Constrained-random verification leverages compute resources and functional coverage technology to provide more testing with less test code development. Setting up a constrained-random test environment, however, can seem like a difficult task, especially when you consider that environments need to be flexible, scalable, and reusable. The infrastructure for constrained-random verification requires more planning and structure, but the benefits in the end are well worth the investment.

Synopsys Verification IP (VIP) leveraging the Universal Verification Methodology (UVM) provides verification engineers with the tools to rapidly build a well-architected, advanced verification infrastructure. Let us start by giving you an overview of the benefits of Synopsys VIP and a brief introduction to UVM. This will supply the background for the discussion of the five simple steps to creating a complete testbench environment for effective constrained-random verification. The concepts and techniques we will explain and demonstrate, and the code examples we will provide, will serve as templates for real application techniques you can use in your designs.

For this article, we will assume you have working knowledge of SystemVerilog and object-oriented programming.

## Benefits of Using Synopsys VIP With UVM

The Synopsys VIP models alone offer many benefits, as they provide proven protocol functionality for verification engineers. When used in a UVM flow, verification teams can attain a number of benefits.

The first benefit is that UVM promotes a modular testbench architecture and provides a standard object-based interface that connects components within a test environment. Better modularity simplifies development and reduces maintenance. Synopsys VIP models provide both protocol functionality and control features in a complete, self-contained package that fully supports the modular architecture of UVM and simplifies the development of UVM testbenches. This gives verification engineers a modular foundation layer over which they can quickly build a robust testbench.

Efficiency of abstraction is another benefit. UVM is based on object-oriented programming (OOP). Synopsys VIP abstracts protocol transactions into objects and provides an object-based interface, allowing engineers to work in logical protocol terms without worrying about implementation details. With protocols becoming more complex, this abstraction is a big boost, as dealing with the details of a standard protocol is time-consuming and does not add value to the end product. Another benefit of the modular, layered approach is that it allows engineers to stack components to create complex systems. For example, a typical webcam transports video data stacked on top of the USB protocol.

Rapid creation of complex tests is the third benefit. While modularity enables the construction of complex test infrastructures, constrained-random verification and efficiency of abstraction allow the easy development of complex tests. Engineers can easily create tests that exercise different scenarios within a given set of constraints. In encapsulating protocol functionality, Synopsys VIP allows engineers to code with abstracted objects where they can easily create tests for intricate and complex combinations of transactions. Engineers can use these sequences to mirror real-world traffic, create stress or corner-case conditions, or simply cover a wide range of conditions. They can create more conditions by simply letting the test run for a longer time.

Increased reuse is another benefit of using Synopsys VIP with UVM. Synopsys VIP models are inherently reusable blocks that all have the same look and feel, simplifying the integration of multiple components. Meanwhile, UVM is architected for maximum reuse, and it fosters testbench code that maximizes reusable components. UVM even provides a template for a standard testbench flow, which engineers can customize to suit their specific needs. The UVM base classes provide reuse through inheritance.

### Introduction to UVM for SystemVerilog

Now that we have described the key benefits of using Synopsys VIP models with UVM, it is time to dive into a more detailed look. We will look at a few basic constructs to gain a conceptual understanding of the basics and get you going on your way to creating more effective testbenches. We'll then dive further into the nuts and bolts of building a first testbench using Synopsys VIP and UVM. We'll show how to apply the methodology and concepts using actual code.

So what is UVM? UVM stands for Universal Verification Methodology. It consists of three things: a set of base classes, a verification methodology, and a modeling approach guideline.

The guiding principles of UVM are to emphasize constrained-random verification, maximize reuse, minimize test-specific code, and enable more testing with less code.

## Verification Methodology

UVM provides a template for an advanced verification methodology. Supporting constrained-random verification is different than using a directed, sequential flow. UVM provides a blueprint methodology so that testbench code is effectively organized for constrained-random verification. And the resulting structure also supports directed testing, so it serves all verification needs.

The shift to object-oriented programming techniques, the dynamic nature of constrainedrandom verification, and the need to develop code efficiently are all encapsulated in the UVM. To achieve its goals, UVM prescribes an overall testbench organization, which impacts the way that testbench code is written. Here are some highlights:

- Most of the code is dedicated to setting up dynamic processes in advance. Everything is already programmed by the time the test is started.

- Test conditions are controlled by constraints instead of procedural code.

- Tests react to significant events dynamically. For example, a testbench must be able to detect the end of the testing sequence since the length of the sequence is not pre-defined. Checking mechanisms are dynamic. Scoreboards or other self-checking mechanisms store information on-the-fly and sometimes perform all checks on-the-fly.

- Objects use the UVM base classes whenever possible to maximize reuse and guarantee interoperability.

- A standard testbench sequence template is used (build-configure-execute-report). Each testbench uses the template but fills in the details according to its needs.

Programming orientation shifts from procedures to objects. We won't discuss this in detail, because it is inherent in the adoption of SystemVerilog and is outside the scope of this article.

#### **UVM Verification IP**

In an object-oriented programming environment, a set of base classes form the foundation for the entire system. Base classes provide common functionality and structure. Because most objects will be derived from them, a well-architected set of base classes is essential to the end goal of an effective programming environment.

The classes provided by UVM are specifically designed for verification. They provide the base functionality that verification engineers need for simulation (such as logging), and they support any sort of verification task. The Synopsys VIP models are based on the same UVM classes that are also available for the end user, allowing easy integration of user code and Synopsys VIP in a verification environment. Further, UVM provides an actual implementation of its base classes and is not simply a set of guidelines or recommendations.

A simulation VIP written in UVM presents a configuration and transaction-level interface that is used by testbench environments and test cases to interact or monitor a design under test (DUT), usually through a signal-level interface. Using a simulation VIP to implement a simulation environment allows engineers to write test cases at a much higher level of abstraction.

#### Agent

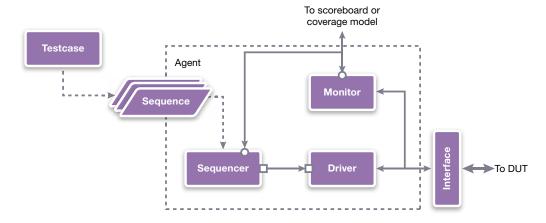

In UVM, a VIP may be called a UVM verification component (UVC) or simply an agent. UVM VIPs are implemented as agents. UVM agents have a well-defined architecture: they encapsulate a sequencer, a driver, and a monitor. In active mode, all components encapsulated by the agent are instantiated and are running. In passive mode, the sequencer and driver are not instantiated and only the monitor is running. We use the uvm\_agent base class to create an agent.

Figure 1. UVM agent architecture

Configuration: An agent is usually configured through a configuration object, passed via the UVM configuration database. The agent configuration object is usually obtained from the environment configuration object.

Sequencer: The sequencer is a component that executes one or more sequences concurrently. A sequence, when executed, creates sequence items (transactions) that the sequencer sends to the driver for execution. The sequencer arbitrates between the different sequences that are being executed in parallel, selecting one to generate its next sequence item (transaction). Once the sequence item is generated, it is then sent to the driver for execution. The sequencer is also responsible for collecting the transaction responses and forwarding them to the appropriate sequence.

Driver: The driver executes transactions (sequence items) as they are submitted by the sequencer according to the semantics of the protocol it implements and the transaction description received from the sequencer. A typical driver drives the signals encapsulated in the interface according to the protocol specification. The actual values driven on data signals, and the relative timing of control signals, will be taken from the corresponding properties in the transaction description. If the protocol allows it, a driver may execute more than one transaction at the same time or in a different order (should the sequencer supply multiple transactions before the previous ones complete their execution).

Monitor: The monitor observes the signals encapsulated in the interface and interprets their transitions and values according to the protocol semantics. It reconstructs transaction descriptors for every observed transaction and publishes them on its analysis port. The published transactions can then be used by a scoreboard to determine if the overall operation of the DUT is functionally correct, or by a coverage model to record which conditions have been applied to the DUT. The monitor also performs protocol-level checks and reports any observed functional or timing violations using warning, error, or fatal messages.

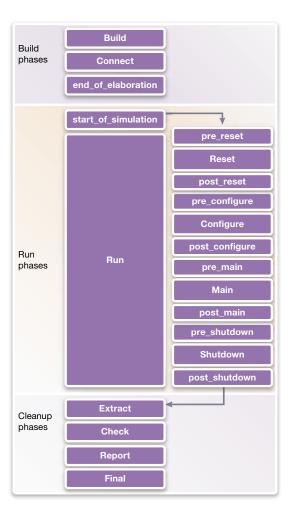

The execution of every test case is divided into several orchestrated or sequential phases. Typical phases include resetting the DUT, configuring the DUT, executing the actual test, and cleanly shutting the DUT. UVM has a well-defined phasing mechanism that can, when properly used, meet the demands of the most complicated test cases. The following figure shows all the different phases through which the UVM structural components are sequenced.

"UVM provides a blueprint methodology so that testbench code is effectively organized for constrained-random verification."

Figure 2. UVM phases

For a Synopsys VIP user, the modeling approach defined by UVM is already incorporated into the models. This means that the models are UVM compliant and will operate seamlessly within a UVM environment.

## Five Vital Steps to Using Synopsys VIP in UVM

Now let's apply a few basic UVM concepts and techniques to quickly achieve a basic constrained-random testbench. The first five steps to using Synopsys VIP and UVM are:

- 1. Create/instantiate a test environment.

- 2. Connect the VIP to the DUT.

- 3. Instantiate and configure the VIP.

- 4. Create a test sequence.

- 5. Create a test.

To illustrate these methods in practical use, we'll draw code snippets from a complete example testbench. The testbench shows typical Synopsys VIP and UVM usage, and it highlights the concepts and techniques described. Although the example code uses Synopsys VIP for the ARM® AMBA® AXI3™ protocol specification, the methods we show here are not specific to the protocol. You can use them with any of the Synopsys VIP models. To obtain the example code, please refer to the instructions at the end of this article.

#### Step 1: Create/Instantiate a Testbench Environment

An environment encapsulates all of the agents, monitors, checkers, and scoreboards necessary to stimulate, observe, and check the correctness of the design under verification. Environments are strictly structural components. They instantiate and connect the various components needed to verify a design, but they do not contain any actual behavior toward accomplishing that verification. An environment is implemented as a class, extended from the uvm\_env base class. The environment class has public members for each of the individual agents, monitors, checkers, or scoreboards it encapsulates. These components are instantiated in the build\_phase() method and are appropriately interconnected in the connect\_ phase() method. An environment class should not implement any run-time phase.

For the Synopsys VIP, this environment encapsulates all of the VIP components and implicitly constructs the required number of protocol agents as specified by its system configuration object. As we will see, the vast majority of code in a UVM testbench is contained in the environment where it can be reused by other tests or projects.

The user inherits structure and base functionality from uvm\_env and yet can still customize where needed. Furthermore, the customization is under the user's control. This is a common theme throughout UVM and the Synopsys VIP models.

```

class test_env extends uvm_env;

svt_axi_system_env axi_system_env;

scoreboard

function void build_phase(uvm_phase phase);

super.build_phase(phase);

... axi system env =

svt_axi_system_env::type_id::create("axi_system_env", this);

sb = scoreboard sb::type_id::create("sb", this);

. . .

endfunction

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

axi system env.master[0].monitor.item observed port.connect(sb.axi

master0_aip);

endfunction

endclass

```

The following are steps to instantiate the AXI™ system environment in your testbench environment.

```

svt axi system env axi system env;

axi_system_env = svt_axi_system_env::type_id::create("axi_system_env", this);

```

In the build\_phase() method, obtain the top-level configuration object (see Step 3) from the configuration database. Instantiate each sub-component (agents, sub-environments, scoreboard), setting the configuration information for each sub-component appropriately. To improve the ability to debug, use the data member handle name as the component instance name when calling create().

"The shift to objectoriented programming techniques, the dynamic nature of constrained-random verification, and the need to develop code efficiently are all encapsulated in the UVM."

```

function void build_phase(uvm_phase phase);

super.build_phase(phase);

if (!uvm_config_db#(tb_cfg)::get(this, "", "cfg", cfg)) `uvm_fatal(...)

master0 = svt_axi_master_agent::type_id::create("master0", this);

uvm_config_db#(svt_axi_master_configuration)::set(this, "master0", "cfg",

cfg.axi_cfg.master_cfg[0]);

...

sb = scoreboard sb::type_id::create("sb", this);

uvm_config_db#(tb_cfg)::set(this, "sb", "cfg", cfg);

endfunction

```

In the connect\_phase() method, connect the analysis ports of the relevant agents to the analysis exports of the scoreboard.

```

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

axi_system_env.master[0].monitor.item_observed_port.connect(sb.axi_master0_aip);

...

endfunction

```

To be reusable in eventual higher-level environments, the top-level environment class should only implement structural and connectivity aspects of the testbench.

#### Step 2: Connecting the VIP to the DUT

The DUT harness instantiates the DUT and provides all of the necessary support to drive and monitor all of its I/O signals. It is responsible for generating clock and reset signals, and for connecting the I/O side of the verification IP to the DUT.

The following are the steps to establish a connection between the VIP to the DUT in your top-level testbench:

Include the standard UVM and VIP files and packages

```

`include "uvm_pkg.sv"

`include "svt_axi.uvm.pkg"

`include "svt_axi_if.svi" //top-level AXI interface import uvm_pkg::*;

import svt_uvm_pkg::*;

import svt_axi_uvm_pkg::*;

```

▶ Instantiate and connect the top-level AXI interface to a system clock

```

svt_axi_if axi_if();

assign axi_if.common_aclk = <system clock>;

```

▶ Connect the top-level AXI interface to the DUT and the AXI system environment dut dut\_inst(axi\_if); uvm\_config\_db#(svt\_axi\_vif)::set(uvm\_root::get(), "uvm\_test\_top. env.axi\_system\_env", "vif", axi\_if);

The uvm\_config\_db command connects the top-level AXI interface to the virtual interface of the AXI system environment. The "uvm\_test\_top" represents the top-level module in the UVM environment. The "env" is an instance of your testbench environment. The "axi\_system\_env" is an instance of the AXI system environment (svt\_axi\_system\_env).

Connect the reset pin of the AXI master and slave agent interfaces to the desired reset signals

```

assign axi_if.master_if[0].aresetn = <User-select Reset Signal>;

assign axi_if.slave_if[0].aresetn = <User-select Reset Signal>;

```

In the sections that follow, the individual steps in the test sequence are shown in detail.

#### Step 3: Instantiating and Configuring the VIP

Synopsys configures Synopsys VIP models using configuration objects that are provided and ready for use. The environment configuration classes are extended from the uvm\_object class. All public members are declared as 'rand' in that class. Additional, sub-environment configurations may also be members of this class. The sub-configurations would be created within the constructor of the top-level configuration object. Engineers can handle configuration objects just like any other objects, so the objects can be randomized and passed as an argument to a method. The objects come with constraints so they adhere to protocol limits. These can be controlled or extended as desired to create specific test conditions, or used as is to produce a wide range of stimulus.

We can customize an AXI system configuration class by extending the AXI system configuration class (svt\_axi\_ system\_configuration) and specifying the required configuration parameters.

#### For example:

```

class cust_svt_axi_system_configuration extends svt_axi_system_configuration;

function new (string name = "cust_svt_axi_system_configuration");

super.new(name);

// Create a single AXI master agent and a single slave agent

this.num masters = 1;

this.num slaves = 1;

// Create port configurations

this.create_sub_cfgs(1,1);

this.master_cfg[0].data_width = 256;

this.slave_cfg[0].data_width = 256;

this.master_cfg[0].id_width = 4;

this.slave_cfg[0].id_width = 4;

endfunction

endclass

```

Once the customized configuration object is created, the instance needs to be passed to the system environment (instance of svt\_axi\_system\_env) in the build phase of your testbench environment.

```

cfg = cust_svt_axi_system_configuration::type_id::create("cfg");

uvm_config_db#(svt_axi_system_configuration)::set(this,

"axi_system_env", "cfg", cfg);

```

Once set, in the build\_phase() method of the testbench environment (see Step 1), obtain the top-level configuration object from the configuration database. You can then use the configuration object values to instantiate each sub-component (agents, sub-environments, scoreboard, etc.).

#### Step 4: Creating a Test Sequence

The object-based interface provided by Synopsys VIP and UVM creates a subtle yet important shift in how constrained-random generation can be used in the context of creating the necessary traffic patterns for the various standard interfaces. Building on the fact that the models abstract protocols into transaction objects, specifying test conditions is a matter of generating constrained-random objects. The shift here is that defining the transactions occurs in protocol terms and uses native language syntax (constraints and assignments), so verification engineers can think in protocol terms, not model details. This abstraction allows a more natural and efficient thought process.

To enable this, the VIP provides a base sequence class for the different protocol agents. For example, the AXI master agent would have the svt\_axi\_master\_base\_sequence and the AXI slave agent the svt\_axi\_slave\_base\_ sequence. You can extend these base sequences to create test sequences for the AXI master and slave agents. The VIP also provides a sequence collection, which essentially is a list of random and semi-directed sequences that extends from these base sequences. These sequences, when executed, create sequence items (transactions) that the sequencer sends to the driver for execution. The sequencer arbitrates between the different sequences that are being executed in parallel, selecting one to generate its next sequence item (transaction). Once it generates a sequence item, it is then sent to the driver for execution.

The sequence item created within a sequence running on a sequencer is a blueprint for randomization and the template for the generated objects. When using Synopsys VIP models, you can manipulate them by extending the provided base transaction (extended from uvm\_sequence\_item) objects and applying your own user-defined constraints. Using the 'factory override' mechanism in UVM ensures that when the transaction is randomized, the user constraints will be used and, through inheritance rules, that the extended objects can be driven onto the driver by the sequencer. Synopsys VIP models also support the addition of user data members in these transaction objects, allowing user customization of the transactions themselves. The details of this are outside the scope of this article.

#### Step 5: Creating a Test

The Synopsys VIP models all share the same features regarding test control. You can create a VIP test by extending the uvm\_test class. In the build phase of the extended class, you construct the testbench environment and set the sequences to run on the respective sequencers and in the relevant phase. In the context of the AXI VIP, you can create and run a simple test as follows:

In the above code snippet, we have used a sequence, axi\_master\_wr\_rd\_sequence\_, which is part of the AXI VIP sequence library to run on the 'main\_phase' of the sequencers of all the master agents configured and instantiated in the AXI system environment. Similarly, the axi\_slave\_mem\_response\_sequence, which is also part of the sequence collection, is configured to run on all the active slaves. Note, you must set a slave response sequence for active slaves in the run phase.

Notice how small the test-specific code is when you use UVM! Most code is in the environment, which is a reusable component. The test-specific code is minimized and as much code as possible is common so it is not replicated unnecessarily. This yields a smaller code base to maintain.

The code shown in this article is from an example testbench, which ships with the AXI3 VIP installation, and is a complete and functional test using the AXI3 Synopsys VIP models. Looking at the entire example we see that with the combination of Synopsys VIP and UVM, constrained-random verification can be performed in a well-architected and efficient manner. The protocol functionality is abstracted by the Synopsys VIP model, allowing you to work at a higher abstraction level. You can use just a small amount of code (~200 lines) to generate a very large set of conditions by controlling constraints and using test execution time instead of code development time. There is a high degree of reuse inherent in the methodology. Test-specific code is minimized with the majority of the code in the environment. Including constraints and configurations, there are only 32 lines of test-specific code!

The concepts described here will hopefully get you started with solid fundamentals and inspire you to learn more. A great next step is to visit the Verification IP web page, where among other things you can view multiple whitepapers, blogs, and webinars to help you in your journey toward the coverage closure of your SoC designs. Happy verifying! ■

#### **About the Author**

Amit Sharma, is a director in the Verification Group in Synopsys India. He is an Electronics and Communications graduate and holds an MBA from the Indian Institute of Management, Bangalore. Amit has 15 years of experience in various facets of functional verification and currently leads the AsiaPAC Corporate Applications Engineering team in deploying emulation technologies, verification IP, and other advanced verification technologies.

#### **EDA Tools**

## Addressing Physical Design Challenges in the Age of FinFET and Smarter Design

Synopsys Insight Staff

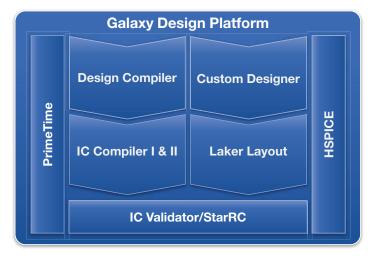

With the mainstream in IC design moving to FinFET processes and with chip architects adding evermore complex functionality to create smarter ICs, engineering teams tasked with performing physical design today have a daunting set of challenges they must address — and they need a trusted, comprehensive physical implementation tool suite like the Galaxy™ Design platform to address them.

Figure 1. The Galaxy Design Platform offers a highly integrated flow of best-in-class physical design tools for the toughest designs on the most advanced silicon processes

"The most fundamental challenge for physical design teams in the age of FinFET is simply dealing with the leap in design complexity," said Mark Richards, senior technical marketing manager at Synopsys. "Design complexity is growing massively as the industry transitions from planar to what is now quickly moving to the third generation of FinFET technologies. Designs are of course bigger, have more on-chip memory, but also have more processors, more types of processors, and more complex clocking schemes to handle low power and of course higher frequencies."

Complexity is very dependent on the application. Whereas a smartphone processor might be considered on the small size these days, a GPU or server processor consists of hundreds of thousands 'step and repeat' processing units. "We've seen as many as half a billion placeable instances on an entire design," stated Richards. "We're seeing thousands of generated clocks running at very high frequencies that we need to balance by ensuring we have the lowest insertion delays," he said. "Managing all of this clock complexity is very challenging, and it's a key trend, which is why we've invested so much in developing the clock handling capabilities within IC Compiler™ II."

Increasingly, design teams have to break down big macros into small macros, which leads to fragmentation in the floorplans. Richards believes that all these challenges impact the entire design flow. "While you can shrink standard cells at each new generation, realistically when you put all these cells together, you can't route them at the new density," he said. "There are so many other things in flight that we need to address through place and route, modeling, improvements to routability, placement technology — there are implications for the entire flow."

"One of the biggest challenges back-end teams face when moving from planar to FinFET is multi-patterning," added Mary Ann White, product marketing director for the Galaxy Design Platform. "It's an essential part of the design flow that enables foundries to print chip feature sizes that are a fraction of the wavelength of light. There are several forms. At 16- and 14-nm, double patterning was sufficient, but as we move down to 10-nm and below, selfaligned double patterning (SADP), triple patterning, and quad or more multiple patterning are essential."

Another significant challenge is dealing with the huge increase in capacitance with 3D FinFET structures, said White. "A lot of our tools have to be updated to effectively extract these capacitances," she said. "The challenge for the design team is how to manage the 2-3x capacitance that FinFET introduces, which can result in more dynamic power consumed. Some of the dynamic power is taken care of by moving to the lower voltage operation — from 0.9V or 0.8V to 0.5V, and in some cases lower, down to 0.35V, our tools — anchored by Design Compiler® and IC Compiler II — have several dynamic power optimization capabilities to help mitigate the effects of the extra capacitance."

"As well as capacitive effects, resistance is going up massively node on node," stated Richards. "The effect of grain/surface scattering at 7-nm is dominating compared to bulk resistivity, which means very high resistance, particularly in the lower metal layers. That in turn means using the multi-pattern layers is very challenging because they're so resistive — you want to get off them as soon as possible. This one issue has implications for design speed and power, timing and accuracy. Having very resistive wires means that the waveforms going into the cell are very different from those coming out of the cell - they're no longer linear, so the characterization becomes much more difficult." Design Compiler Graphical and IC Compiler II have layer awareness built-in such that critical nets are promoted to upper metal layers that are much less resistive.

#### **Transparency and Entitlement**

"Synopsys aims to make the physical design issues for FinFET as transparent to users as possible," said White. "When you move to a FinFET flow, it's very similar to the planar-based flow that experienced users know well."

Richards adds that FinFET processes promise a lot in terms of power, area, and performance benefits. However, whether design teams get those benefits or not when it comes to the real design really depends on the tool flow. "Our aim is to provide the entitlement part of the equation to design teams. By providing advanced flows and methodologies, we aim to get as close to fulfilling the promise as possible," said Richards.

Two of the more important benefits of moving to FinFET include the ability to use higher transistor drive currents and to operate at a lower voltage. Higher drive current and ever narrowing wires means higher current density, which can lead to electromigration (EM) issues. Synopsys can verify and fix EM issues at the chip, cell, signal, and transistor levels. The move to a lower voltage itself brings other challenges such as process variation and waveform distortion that have to be accounted for. Synopsys' Galaxy Design platform has several techniques - such as parametric on-chip variation (POCV) and advanced waveform propagation optimization and analysis that take care of these low voltage effects.

"Design complexity is growing massively....

Designs are of course bigger, have more on-chip memory, but also have more processors, more types of processors, and more complex clocking schemes to handle low power and of course higher frequencies."

### **Balancing Accuracy and Runtime**

"We have to increase tool accuracy for every new node if we're going to deal with all of these engineering tradeoffs — that's a constant challenge we work to address," stated Richards.

While the Synopsys PrimeTime® tool is the gold standard for timing, Synopsys aims to align its implementation platform IC Compiler II, as closely as possible to that standard.

"Christmas always falls on December 25th, so unfortunately chip implementation schedules aren't moving to accommodate the rise in complexity," said Richards. "In practical terms, what that means is that as well as increasing accuracy, we need to maintain or even improve runtimes as instance counts grow between nodes. Developing tool flows with increased automation, accuracy, and runtime enables design teams to do more 'what-if' exploration, which leads to better quality of results."

Richards notes that another layer of complexity comes as a result of customers looking to differentiate their designs by implementing more advanced power management strategies, like selectively powering down different blocks and running in different modes of operation. Supporting the concept of "dark silicon," where design teams gate modules to slow them down or turn them off, requires the use of multiple design techniques, including clock gating and multi-voltage design. Automating such low-power design techniques is key to meeting project schedules.

Richards notes that from conception, one of the key motivations for designing and building IC Compiler II from the ground up was to dramatically improve turnaround time and capacity.

"The writing was on the wall many years ago about the key challenge for the industry: managing ever-growing design size and complexity. The vision for IC Compiler II before we started any coding was to manage high-capacity designs, minimize turnaround times, and reduce the number of design iterations required while maintaining the best possible quality of results," commented Richards. "It's all about enabling design teams to hit their market window even as designs dramatically scale in size and complexity."

#### **Risk-Reward Tradeoffs**

A key decision for chip architects nowadays is whether to make an IP block that is completely optimized for power, performance, and cost for a specific application, or to trade off that approach against implementing a more general-purpose block.

"In some ways this is a 'risk vs. reward' decision," said Richards. "If you create the best design but you miss the market for a specific application, it's likely there's nothing you can do with the chip — it's useless. What we see in some applications is design teams balancing what they commit to an IP block (so it has the lowest power possible) and what they leave programmable (so that they can adapt the design to meet evolving standards)."

"5G, or LTE, is a perfect example of this design dilemma," said Richards. "LTE is a moving target; there is no current standard as it's being developed year on year," he noted. "How you commit to silicon will impact your business. If you go for a fixed function, it isn't going to last very long so you need a lot of programmability. You could go all the way to an FPGA implementation — it's the traditional make vs. buy tradeoff — but it's becoming a more finely balanced decision and at the same time an opportunity to differentiate."

#### Masking Complexity

In moving to a FinFET-enabled flow, another of Synopsys' aims is to help customers become more productive by managing the physical design complexity on their behalf.

"Our job is to hide the challenges as much as possible," stated White. "Our long-established relationships with leading foundries like TSMC, Samsung Foundry, GLOBALFOUNDRIES, Intel Custom Foundry, and others enables us to work very closely with them well in advance of the processes becoming available. We identify the challenges and then figure out the best way to solve them."

A good example is routing, Richards added. "The layout engineer shouldn't have to worry about whether a route is on mask A or mask B when we're using multi-patterning, for example. We also measure our success in how evolutionary it is to move from say a 28-nm design flow to a 16-nm design flow. We don't expect engineers to have to spend six weeks re-learning how to do place and route. They can focus on the tasks that they already know how to do well - or example, importing the RTL netlist efficiently. The challenges are getting more complex, so we fully expect to continue to develop our tools to do more and more of the heavy lifting as we move to 10-nm and 7-nm process nodes."

How Synopsys manages each specific issue depends on what approach will get the best from the technology while keeping the flow easy to use.

"We maintained a colorless approach to routing at 16-nm, because it simplified the process for the end user at the routing stage," stated Richards. "We get the IC Validator tool to separate the colors later on. To the user, it looks like regular routing - they don't have to worry about the two masks. Another benefit of this approach is that there is a lot more flexibility from a routability perspective. For example, a colorless macro cell has a lot more scope to move freely, because you don't have to maintain the alignment between pins and tracks of the same color. Your design flow looks just like a 28-nm flow, and the tools make sure the design is decomposable later on in the flow - you don't have to worry about it."

However, at 10-nm, the process demands shift again and for these technologies the Synopsys flow supports colored routing in order to make life simple for the engineer while optimizing for the constraints of each process.

## **Accelerating Turnaround Time**

The subdivided resistance and capacitance inherent to FinFET 3D transistors demands more sophisticated modeling and analysis than planar structures.

"We ensure ultimate model accuracy within the signoff tools, but for physical implementation we maintain a higher level of abstraction that enables the fastest turnaround times," commented Richards. "Our team developing the physical implementation tools works very closely with our colleagues working on the PrimeTime static analysis and StarRC™ parasitic extraction tools to ensure we take what they have and model what we need to provide the appropriate levels of accuracy with the best possible runtimes." See Figure 2.

"Synopsys aims to make the physical design issues for FinFET as transparent to users as possible.... When you move to a FinFET flow, it's very similar to the planar-based flow that experienced users know well."

Figure 2. IC Compiler II features 10x faster throughput to accelerate product schedules on the most complex designs.

The latest modeling approach for advanced process nodes, the Liberty™ Variation Format (LVF), targets parametric on-chip variation. Design Compiler, IC Compiler II, PrimeTime®, StarRC™, and other tools within the Synopsys ecosystem look at this variation in terms of analysis and in certain cases can optimize using these kind of models. LVF uses statistical analysis to offer a less pessimistic modeling approach for advanced technologies using ultra-low voltages — particularly FinFET nodes at 10- and 7-nm and below.

#### Convergence to a Realizable Design

Synopsys customers are reaping the benefits of using an integrated flow, especially for more advanced processes. For example, modifying the layout after implementation affects all design targets, including timing, power, and signal integrity. In-Design physical verification provides a push-button flow for signoff-quality metal fill and design rule checking (DRC) inside IC Compiler where timing can still be considered. IC Validator In-Design physical verification combines timing awareness and signoff accuracy to speed up tapeout schedules.

"High-density current can cause electromigration problems, which is why we've designed PrimeRail to work within IC Compiler II as well." commented White, "You can do what-if analysis on IR drops and electromigration to see any potential hotspots as you manipulate the layout rather than doing the analysis as a batch process. Co-design with Custom Compiler™ allows you to do custom design on signal routes, for example, all within the IC Compiler II environment."

"We see significant benefits from having common engines across our tools for dealing with advanced processes," added Richards. "Sharing a common view of the flow across tools means that the design convergence is much better. If my synthesis tool tells me the design is fine and then I go to place and route and find it's not even routable, then I've got to go back to re-do all my synthesis. By using a shared body of knowledge to create common timing engines, common router technology, consistent models, and so on, we ensure the results out of each stage of the design flow are consistent and there are no surprises. And the bottom line is that convergence correlates directly with project timescales."

An added advantage of the Synopsys Galaxy flow is that leading foundries use Synopsys' Technology Computer-Aided Design (TCAD) tools to develop and optimize their semiconductor processing technologies and devices.

"Having TCAD within the Synopsys portfolio is a bit like having a cousin who knows someone in the band," stated Richards. "You get to hear the latest music before anyone else does. Through TCAD we had awareness of FinFET technology probably 10 years before customers were designing with it and are able to align our tools with the processes. Having the inside track through close ties with foundries - and academia - is vital if we're to keep our customers hitting the ground running with the latest technology." ■

To learn more about the Galaxy Design Platform for implementation, click here!

## Multi-Level Physical Hierarchy Floorplanning vs. Two-Level Floorplanning

Steve Kister, Technical Marketing Manager, Synopsys

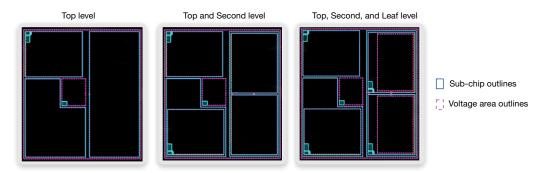

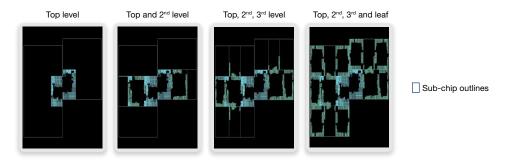

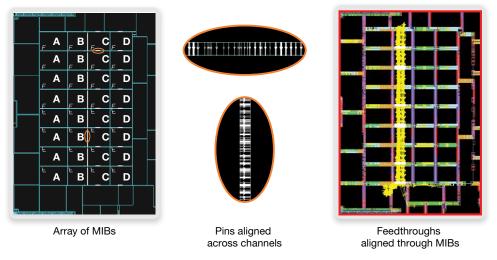

Today's SoC designs require hierarchical layout methodologies that span multiple levels of physical hierarchy. Many of today's physical design tools only handle two levels of physical hierarchy at a given time, limiting potential quality of results (QoR) that design teams can achieve in the time they have scheduled for layout. Synopsys' IC Compiler™ II provides automation for designs with multiple levels of hierarchy. This minimizes time to results, provides best QoR, and maximizes productivity of physical design teams.

Let's look at the challenges inherent with tools limited to two levels of hierarchy, discuss why design teams need multi-level physical hierarchy floorplanning, and explore how IC Compiler II addresses the challenges of floorplanning modern SoCs.

#### The Challenges of Floorplanning Large, Complex SoCs

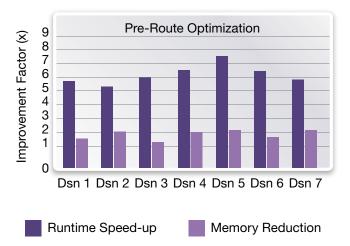

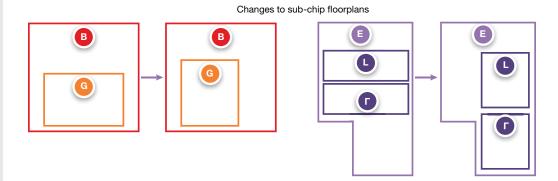

The operating speeds and capabilities of large, complex SoC designs are striking, and the task of physically implementing these designs is daunting. Today, design teams are dealing with 100s of millions of gates — tens of millions of placeable instances. To manage this complexity, physical design teams use hierarchical implementation methodologies to divide a single chip into sub-chips. Often the sub-chips are so big and complex that they too must be divided into even smaller sub-chips (Figure 1). Using three, four, or even five levels of physical hierarchy to implement a design is becoming the norm.

Figure 1. Physical floorplan divided into three levels of sub-chips

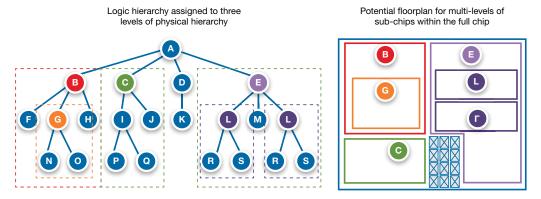

Design teams floorplanning today's largest and most complex SoCs are finding it increasingly difficult to perform and manage physical planning with tools limited to two levels (top and block) of physical hierarchy. A two-level-at-a-time physical implementation flow requires designers to employ a recursive flow. The added flow complexity and data management impacts the productivity of design teams and delays design schedules. Truly supporting multi-level physical hierarchal planning and layout is an opportunity for planning, place, and route tools to improve designer productivity and efficiency, and to minimize design schedules.

## Pitfalls of Recursive, Two-Level-At-a-Time Hierarchical Methodologies

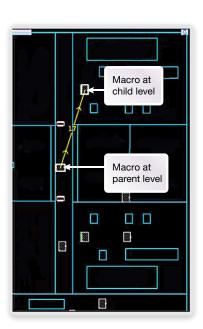

With a two-level-at-a-time physical implementation flow, design teams are forced to set block shapes, set pin placement for each block, and budget block timing constraints one level at a time. This makes it very hard for design teams to plan all of the lower levels within the context of the full chip design. Instead, they are forced to plan lower levels in the context of constraints defined on each level's parent level parent (Figure 2).

Figure 2. Multi-level physical floorplan divided into several two-level (top and block) floorplans

The shapes, pin placements, and budgets set at a given parent level become hard constraints for the child level of the design. If the design team makes a change to one of the blocks at a lower level, that change can impact the top level of the design. To address such a change, teams have to consider how a given change will impact other levels and what extra work will be required to make those changes. Simply deriving a plan to implement one of these changes takes a lot of negotiation between design team members and can be quite complex. The exercise can often lead to schedule slippage.

Indeed, design teams employing a two-level-at-a-time physical implementation flow spend a significant amount of their overall design time managing data and tracking tasks. For example, to manage design complexity and minimize memory use, teams will convert the children of a given level into black boxes—even if they have access to the netlist data. They often boil down area requirements to an educated engineering guess and must manually account for any constraints on shapes or sizes to accommodate hard macros within the child block. Teams take ownership of creating black-box models and the subsequent tasks of replacing blackbox models with real netlist data at later points in the flow.

There is the potential for designers working at the child level to create and compound problems unknowingly. Consider two designers each working on a sub-chip that is connected through logic at a parent level. Each designer may choose to move content within their subchip to improve routability and timing. However, when they put these into the context of the full chip, the designers may have created timing paths that cannot be closed easily (Figure 3).

"Using three, four, or even five levels of physical hierarchy to implement a design is becoming the norm."

Sub-chip floorplans in full chip. Time of flight from G to L increased.

Figure 3. Example of sub-chip changes that can make top-level closure more difficult

Another level of complexity is introduced when teams use a multiply instantiated block (MIB). An MIB is a physical block that design teams intend to use multiple times in a given design. Design teams creating a given MIB must consider where and how they will use the MIB throughout their layout. For example, when design teams intend to use MIBs within lower level sub-chips, they must consider the requirements for each unique environment when defining the shape, size, pin placements, and timing constraints needed to implement the MIB. Adding to the complexity of multi-level physical hierarchy planning, MIBs may be instantiated at any hierarchical level. So, once again, design team members need to spend cycles planning where to use MIBs within multiple sub-chips.

These pitfalls and others are the source of wasted time and lost QoR in designs. Now let's explore a better way of dealing with the hierarchical complexities of today's designs.

## IC Compiler II Provides Multi-Level Physical Hierarchy Planning

Synopsys IC Compiler II features a new data model with native physical hierarchy. Most physical design tools were created with a flat database and physical hierarchy was added later as a quick competitive response. However, native physical hierarchy provides significant advantages for multi-level physical hierarchy planning and implementation. All engines—shaping, placement, routing, and timing to name a few—quickly access the specific data relative to physical hierarchy that they need to perform their function.

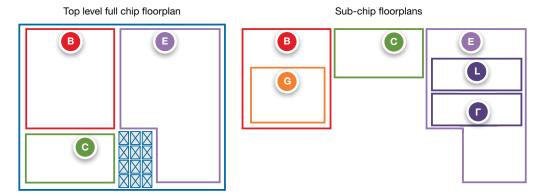

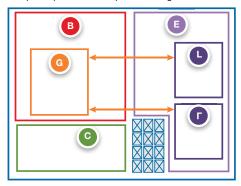

For example, consider shaping. In Figure 4, the shaper needs to know the target area for each sub-chip, aspect ratio constraints dictated by hard macro children, and interconnect that exists at sibling-to-sibling, parent-to-child, and child-to parent interfaces. If the design is a multi-voltage design, the shaper needs target areas for voltage areas. These needs add more constraints for the shaper to deal with in the design. For multi-level physical hierarchy planning, shaping constraints that exist for lower level sub-chips translate up the hierarchy in the form of shaping constraints on parent sub-chips. The shaper does not need

to know about the full netlist content that exists within each sub-chip or block. Synopsys constructed IC Compiler II's database with this idea in mind, providing engines with the specific data required for their particular function. For multi-voltage designs, IC Compiler II reads UPF and stores appropriate data within sub-chip levels. The engines pull data from the database to calculate targets based on natural design use or pull user-defined attributes specifying targets.

Figure 4. IC Compiler II multi-level shaping results

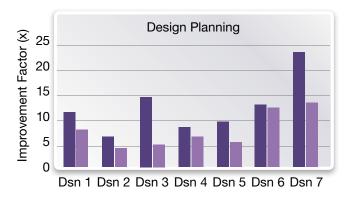

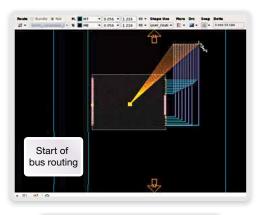

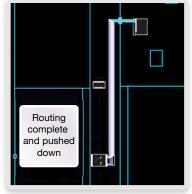

Synopsys built the new data model to support distributed processing architectures. IC Compiler II engines split their jobs, or parts of their jobs, into multiple processes. As shown in Figure 5, cell placement is a good example of this synergy.

After shaping, the placement engine sees a global view of data flow interconnect paths at physical hierarchy boundaries and connectivity to macro cells. With this information, macros are placed for each sub-chip at each level. Understanding relative location requirements of interconnect paths at boundaries ensures there are resources available at the adjacent sub-chip edges to accommodate interconnect paths. The placer anticipates the needs of hierarchical pin placement and places macros where interconnect paths do not require significant buffering to drive signals across macros.