AI驱动的设计应用

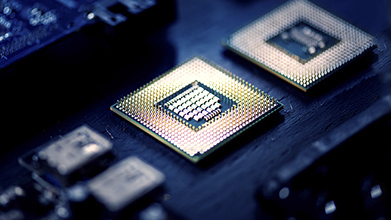

随着数智时代的到来,智能设备的普及度越来越高,用户受到网络攻击的风险和频率也在不断增加。然而,漏洞不只是存在于软件中,硬件中也一样存在。

实际上,随着系统变得越来越复杂,硬件可能会成为不法分子实施攻击的突破口。多芯片设计越来越受欢迎,攻击面也在不断扩大。

安全性现已成为半导体行业关注的焦点,保护片上系统(SoC)接口及相关数据的安全可以防止不法分子访问、删除或以其他方式操纵这类数据。无论是在高性能计算(HPC)、移动通信、物联网领域还是在汽车SoC中,在保护数据的同时还需要优化安全实现,以保持接口的性能,同时减少对延迟和面积的影响。

DDR等高带宽接口正在迅速增多,接口速度也一代比一代快。要想保护数据,就需要保护多个重要领域,其中一个关键部分是片外动态随机存取存储器(DRAM)。

过去十年里,先是学术研究人员提醒可能会出现Rowhammer攻击,接着谷歌的Project Zero又发现了另一个名为RAMbleed的漏洞,这两个漏洞都是DRAM特有的。DRAM漏洞可能会在现实场景中被利用,因此务必要防范Rowhammer、RAMbleed和冷启动等攻击,以免不法分子读取或损坏数据,或检索到对安全至关重要的加密密钥。随着信息传播速度越来越快,系统越来越复杂,风险也变得越来越高。因此,数据保护应当作为硬件设计的重要一环,宜未雨绸缪,切不可亡羊补牢。

本文将进一步介绍黑客如何通过DRAM设备破坏数据和窃取信息,以及在SoC中保护DDR接口安全时可以考虑的一些策略。

存储器攻击原理

下面列举一些DRAM特有的安全漏洞:

- Rowhammer:采用Rowhammer策略的攻击者旨在修改或破坏数据。Rowhammer攻击会高速重复读取存储器行中的数据,导致相邻行内页表条目中的位发生反转(从1到0或从0到1)。谷歌Project Zero团队表示,攻击者可以通过这种方式,对整个物理存储器进行读写访问。随着尺寸不断缩小,DRAM芯片更易受到这类攻击,因为晶体管更密集地堆积在一起,导致在这种攻击过程中发生溢出的风险变得更高。

- RAMBleed:RAMBleed在数据跨系统传输时窃取数据。RAMBleed攻击与Rowhammer攻击原理相同,但会读取信息,而不是修改信息,因此对存储器中数据的机密性造成了威胁。通过RAMBleed攻击方式,攻击者可以从DRAM中提取信息。

- 冷启动攻击:在这种情况下,攻击者可以实际接触到系统。他们可以借此对特定系统进行硬重置,访问启动前的物理存储器数据来检索加密密钥,并造成严重破坏。

通过设计保护存储器接口

无论是在本地还是云数据中心,存储资源及存储其中的数据均由存储器和存储安全加以保障。随着市场对更大容量以及更快访问与处理速度的需求不断增长,开发者转向采用高性能、低延迟的存储器加密解决方案,以便在采用最新一代DDR、LPDDR、GDDR和HBM存储器接口时,能够在保持性能的同时保护数据。

纠错码(ECC)曾经是一种很受欢迎的保护缓解策略,但它只能提供有限的恢复能力。ECC并不能提升安全性,反而还会留下更多未被发现的漏洞,是一种不成熟的存储器完整性保护方法。开发者通常会在找到合适的加密算法之前,使用ECC作为权宜之计。

要保护存储器接口,最好是利用基于标准的加密技术,通过设计解决数据的保密性和完整性问题。例如,通过使用AES-XTS加密来实现数据保密性,可以防范Rowhammer攻击。奇偶校验/ECC只能发现1到2个位翻转问题,而加密可以覆盖所有位。经过加密后,写入存储器的数据看起来更像是随机数据,因此Rowhammer攻击几乎毫无用武之地。借助存储器加密并适当刷新的密钥,也可以防范RAMBleed和冷启动攻击。除了确保数据保密性外,开发者还可以使用哈希加密算法等策略来保证数据真实性,确保数据没有被不法分子修改,从而增强安全性。

从一开始就将安全性作为DDR接口设计的一部分同样存在挑战。其中一个挑战是安全性需要做到万无一失,因为只要有一个薄弱环节,就可能会危及整个系统及其中的数据。例如,务必要在SoC的可信/安全区域中生成和管理密钥,并通过专用通道分发给加密模块。另外,整体安全架构还需要考虑到密钥的回读保护和控制配置。

另一个挑战是,存储器加密是有代价的,包括会影响功耗、性能、面积(PPA)和延迟。开发者需要确保DDR接口设计既安全又符合标准,同时还要高度优化。

我们已经见证了完整性和数据加密(IDE)安全策略在PCI Express®(PCIe®)和Compute Express Link(CXL)接口中的迅速普及,现在DDR和LPDDR等存储器接口也将经历类似的发展轨迹。科技在不断发展变化,开发者设计出更智能的解决方案,罪犯分子也变得越来越狡猾。不管选择哪种安全策略,都应确保能够适应不断演变的威胁环境。

保障SoC中DDR接口安全的几种策略

以下几种策略可以帮助保护SoC中的DDR接口:

- 设计安全的基础架构,包括利用控制面板来实现身份验证和密钥管理,以及利用数据层来确保数据加密的完整性。

- 遵循相关标准。存储器利用各种基于标准的加密算法(比如各种密钥长度的AES-XTS)来确保数据保密性,如NIST SP800-38E中所述。

- 实施高度优化的解决方案,确保可以有效地进行扩展,以支持存储器接口的最新带宽要求。利用流水线架构,实现高效的调整计算、密钥刷新和低延迟。考虑采用各种优化选项,例如在一个循环周期运行多个AES轮次,并使用特定的AES S盒实现来尽可能优化面积或提高频率。

- 支持按区域加密/解密,为各种用例提供灵活性。

- 在安全的环境中生成和管理密钥。存储器加密解决方案需要控制面组件来进行身份验证和管理。通常,这可以通过使用具有信任根源的安全隔离区来解决。安全隔离区需要支持通过固件更新进行调整,以帮助确保密钥管理策略经得起未来的考验,包括算法的潜在变化。

在保护DRAM数据方面,一种解决方案是先使用密钥对数据进行加密,然后再发送到DDR控制器,但这种方法并不理想,因为加密模块必须管理大量操作,以确保数据包大小合适。例如,当应用程序向存储器中写入一个字节的数据时,加密模块需要读取相应存储器位置,并入新的字节,最后再写回存储器中。加密模块与存储器相距越远,要管理的东西就越多。这不仅影响性能预算(对于提高存储器带宽来说代价太高),还必须注意性能下降问题,因为要在SoC上传输数据。

最佳的解决方案是在DDR或LPDDR控制器内紧密耦合加密/解密功能,从而尽可能地提高存储器效率并降低总体延迟。同时,控制器需要尽可能地靠近存储器。

完整的新思科技IME安全模块保障DDR/LPDDR的数据安全

新思科技适用于DDR/LPDDR的内嵌存储加密(IME)安全模块有助于确保数据保密性,让数据在通过存储器接口传输或存储在片外存储器中时都安全无虑。该解决方案基于AES-XTS算法,符合相关标准和认证要求,而且开箱即用,能够让包括新思科技DDR5或LPDDR5控制器在内的存储器控制器实现高效吞吐量。它支持AES-XTS的所有密钥大小,包括128位、256位密钥,并支持可扩展的128位、256位和512位数据路径。IME安全模块通过按地址或边带选择密钥提供了按区域保护存储器的功能,不仅延迟非常低,而且可以针对特定应用进行调整,从而获得最佳PPA。DDR5和LPDDR5控制器中实现了存储器加密,不仅能够帮助开发者节省并优化性能预算,而且延迟非常低。

随着我们的世界越来越频繁地在云端运行,市场对虚拟化的需求一直在不断增长,存储器保护中也需要充分考虑到这一情况。新思科技的IME安全模块能够管理不同虚拟环境中不同区域的数据保护,非常适合支持各种云计算虚拟化环境。

除了DDR/LPDDR安全接口外,新思科技还为各种使用广泛的协议提供完整的标准化安全接口解决方案,具体协议包括PCIe、CXL、HDMI、DisplayPort、USB Type-C和以太网。这些解决方案能够满足最具挑战性的要求,让开发者能够在其SoC中快速实现所需的安全性,从而降低安全风险并缩短产品上市时间。