ASIP Designer

Application-specific instruction-set processors (ASIPs) rely on similar techniques as used in the design of hardware accelerators to achieve high performance and low power: heavy use of parallelism and specialized datapath elements. Yet ASIPs retain software programmability within their application domain, resulting in C/C++-programmable processors and accelerators with the lowest power possible.

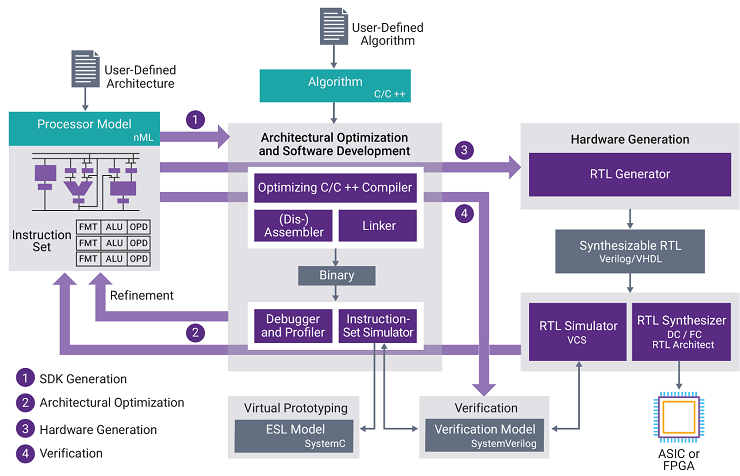

Synopsys’ ASIP Designer™ is a tool suite that brings ASIP design within easy reach of every SoC team. Key capabilities include rapid exploration of architectural choices, generation of an efficient C/C++-compiler based software development kit that automatically adapts to every architectural change, and automatic generation of power and area-optimized synthesizable RTL.

Register for ASIP Designer online training for a deep dive into the concepts, languages and files that are used to capture a processor design.

ASIP Designer's patented technology supports the following features:

- Modeling of ASIP instruction-set architectures in the nML processor description language. nML is a high-level definition language for describing a processor architecture and instruction set (ISA). nML offers designers the abstraction level of a programmer's manual of a processor. Also, with nML the ASIP’s periphery can be modeled in a cycle- and bit-accurate way. nML offers unprecedented architectural breadth, enabling IP development for almost any vertical market.

- Unique compiler-in-the-loop™ technology, enabled by the automatic generation of a comprehensive software development kit (SDK) for each ASIP modeled in nML, containing the following components:

- An optimizing compiler, recognized for its efficient code generation and quick and automatic retargetability to new ASIP architectures. The compiler supports C (optionally extended with user-defined data types and operators using C++ classes and function overloading), C++, and OpenCL C (OpenCL kernel language). The compiler can cope well with architectural peculiarities of DSP cores. It supports instruction-level and data-level parallelism, deeply pipelined instructions, specialized arithmetic functions, custom data-types, specialized address generation units, heterogeneous register structures, and various degrees of instruction encoding (ranging from VLIW to highly encoded instruction sets).

- A linker that builds an executable file from separately compiled Elf/Dwarf object files for different C functions.

- An assembler and disassembler that translates machine code from assembly into binary format and back.

- A fast instruction-set simulator, offering both cycle-accurate and instruction-accurate abstraction levels generated from the same nML model, and easy integration into cycle-accurate and transaction-level virtual prototypes.

- A flexible (multicore) debugger, which can be used in connection to both instruction-set simulators and on-chip debug hardware (via JTAG).

- Multi-faceted profiling capabilities to analyze the instruction-set architecture for hot-spots and to drive the architectural optimization process.

- Automatic generation of a power and area efficient hardware implementation of each ASIP, in synthesizable Verilog or VHDL. A JTAG interface and a debug controller can optionally be generated, to support on-chip debugging.

- Multi-faceted verification capabilities, including the automatic generation of ASIP-specific test programs in C and assembly code.

ASIP Designer comes with a wide range of example ASIP designs, with highly differentiating architectures provided in nML source code. This enables designers to quickly start to create their own ASIP targeting their specific application requirements.

MP Designer

For the design of multicore SoCs, Synopsys offers MP Designer™, a tool suite to assist in mapping sequential single-threaded application code written in C into multi-threaded software for a multicore subsystem.

Register for ASIP Designer online training

![]() ASIP Designer - Application-Specific Processor Design Made Easy Brochure

ASIP Designer - Application-Specific Processor Design Made Easy Brochure![]() ASIP Designer: Design Tool for Application-Specific Instruction-Set Processors Datasheet

ASIP Designer: Design Tool for Application-Specific Instruction-Set Processors Datasheet

|

| Introduction to Synopsys ASIP Designer Designing your own processor is time-consuming and resource intensive, and it used to be limited to a few experts. But Synopsys’ ASIP Designer tool allows you to design your own specialized processor within your deadline and budget. Watch this video to learn more. |